# UNIT - I

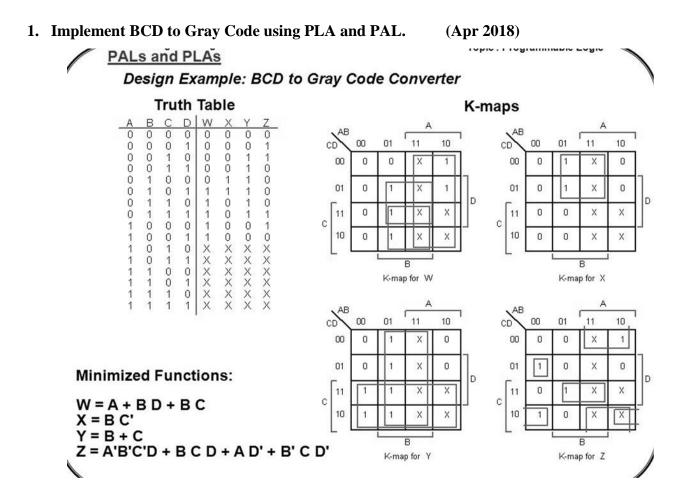

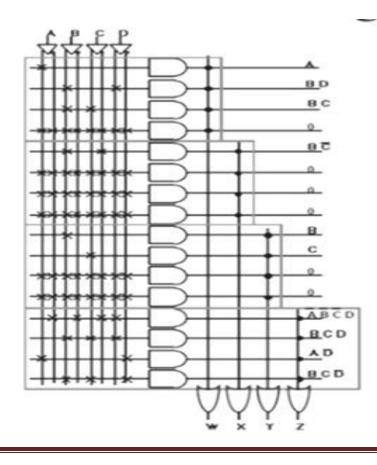

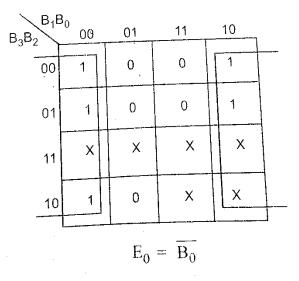

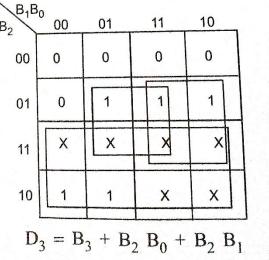

# **BASIC CONCEPTS**

Review of number systems-representation-conversions, Review of Boolean algebra- theorems, sum of product and product of sum simplification, canonical forms min term and max term, Simplification of Boolean expressions-Karnaugh map, completely and incompletely specified functions, Implementation of Boolean expressions using universal gates, Tabulation methods.

# Introduction

Basically there are two types of signals in electronics,

- i) Analog It is a continuous wave that keeps on changing over a time period.

- ii) Digital It is discrete in nature.

# Digital systems:

# Advantages:

- Digital systems are interfaced well with computers and are easy to control with software.

- New features can often be added to a digital system without changing hardware.

- Often this can be done outside of the factory by updating the product's software. So, the product's design errors can be corrected after the product is in a customer's hands.

- Information storage can be easier in digital systems.

- ✤ The noise-immunity of digital systems permits data to be stored and retrieved without degradation.

- In a digital system, as long as the total noise is below a certain level, the information can be recovered perfectly.

## Disadvantages:

- In some cases, digital circuits use more energy than analog circuits to accomplish the same tasks, thus producing more heat as well. In portable or battery-powered systems this can limit use of digital systems.

- Digital circuits are sometimes more expensive, especially in small quantities.

- For example, light, temperature, sound, electrical conductivity, electric and magnetic fields are analog.

# NUMBER SYSTEMS – DECIMAL, BINARY, OCTAL, HEXADECIMAL

# **\*** Discuss the various number system conversions with examples.

Many number systems are in use in digital technology. The most common are the decimal, binary, octal, and hexadecimal systems.

Types of Number Systems are

- Decimal Number system

- ✤ Binary Number system

- ✤ Octal Number system

- ✤ Hexadecimal Number system

#### **Table: Types of Number Systems**

| DECIMAL | BINARY | OCTAL | HEXADECIMAL |

|---------|--------|-------|-------------|

| 0       | 0000   | 0     | 0           |

| 1       | 0001   | 1     | 1           |

| 2       | 0010   | 2     | 2           |

| 3       | 0011   | 3     | 3           |

| 4       | 0100   | 4     | 4           |

| 5       | 0101   | 5     | 5           |

| 6       | 0110   | 6     | 6           |

| 7       | 0111   | 7     | 7           |

| 8       | 1000   | 10    | 8           |

| 9       | 1001   | 11    | 9           |

| 10      | 1010   | 12    | А           |

| 11      | 1011   | 13    | В           |

| 12      | 1100   | 14    | С           |

| 13      | 1101   | 15    | D           |

| 14      | 1110   | 16    | E           |

| 15      | 1111   | 17    | F           |

# Table: Number system and their Base value

| Number Systems |      |                                 |  |  |

|----------------|------|---------------------------------|--|--|

| System         | Base | Digits                          |  |  |

| Binary         | 2    | 0 1                             |  |  |

| Octal          | 8    | 0 1 2 3 4 5 6 7                 |  |  |

| Decimal        | 10   | 0 1 2 3 4 5 6 7 8 9             |  |  |

| Hexadecimal    | 16   | 0 1 2 3 4 5 6 7 8 9 A B C D E F |  |  |

#### Number system Conversions:

Converting from one code form to another code form is called code conversion, like converting from binary to decimal or converting from hexadecimal to decimal.

#### **Binary-To-Decimal Conversion:**

Any binary number can be converted to its decimal equivalent simply by summing together the weights of the various positions in the binary number which contain a 1.

*Example:* Convert 10110<sub>2</sub> into a decimal number.

The decimal equivalent number is given as:  $1 \times 2^4 + 0 \times 2^3 + 1 \times 2^2 + 1 \times 2^1 + 0 \times 2^0$  = 16 + 0 + 4 + 2 + 0 $= 22_{10}$ .

**Decimal to binary Conversion:** Convert 25<sub>10</sub> to Binary.

| Division | Remainder             | Binary                    |

|----------|-----------------------|---------------------------|

| 25/2     | = 12 + remainder of 1 | 1 (Least Significant Bit) |

| 12/2     | = 6 + remainder of 0  | 0                         |

| 6/2      | = 3 + remainder of 0  | 0                         |

| 3/2      | = 1 + remainder of 1  | 1                         |

| 1/2      | = 0 + remainder of 1  | 1 (Most Significant Bit)  |

| Result   | 2510                  | = 11001 <sub>2</sub>      |

Binary to octal: Convert 100 111 010<sub>2</sub> to octal.

Example:  $100\ 111\ 010_2 = (100)\ (111)\ (010)_2 = 4\ 7\ 2_8$

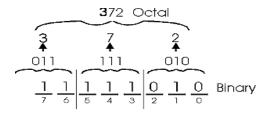

Octal to Binary: Convert 372<sub>8</sub> to Binary. 372 Octal 372 Octal 372 Octal 372 Octal 372 Octal 111 010 $1\frac{1}{7} \frac{1}{6} \frac{1}{5} \frac{1}{4} \frac{1}{3} \frac{0}{2} \frac{1}{1} \frac{0}{0}$  Binary

#### Decimal to octal: Convert 177<sub>10</sub> to Binary.

| Division | Result                | Binary                    |

|----------|-----------------------|---------------------------|

| 177/8    | = 22 + remainder of 1 | 1 (Least Significant Bit) |

| 22/ 8    | = 2 + remainder of 6  | 6                         |

| 2 / 8    | = 0 + remainder of 2  | 2 (Most Significant Bit)  |

| Result   | 177 <sub>10</sub>     | = 261 <sub>8</sub>        |

| Binary   |                       | $= 010110001_2$           |

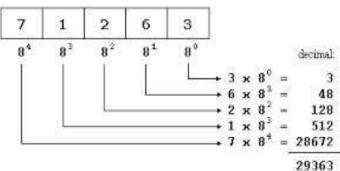

*Octal to Decimal: convert* (71263)<sub>8</sub> *to Decimal.* **Example:**

**Decimal to Hexadecimal:** Convert 378<sub>10</sub> to Hexadecimal.

| Division | Result                 | Hexadecimal                 |

|----------|------------------------|-----------------------------|

| 378/16   | = 23 + remainder of 10 | A (Least Significant Bit)23 |

| 23/16    | = 1 + remainder of 7   | 7                           |

| 1/16     | = 0 + remainder of 1   | 1 (Most Significant Bit)    |

| Result   | 37810                  | $= 17A_{16}$                |

| Binary   |                        | $= 0001 \ 0111 \ 1010_2$    |

Binary-To-Hexadecimal: Convert 1011 0010 1111<sub>2</sub> to Hexadecimal.

Example:  $1011\ 0010\ 1111_2 = (1011)\ (0010)\ (1111)_2 = B\ 2\ F_{16}$

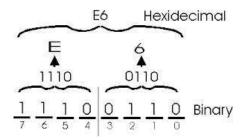

*Hexadecimal to binary: Convert E*6<sub>16</sub> *to Binary.*

# Octal-To-Hexadecimal Hexadecimal-To-Octal Conversion:

- ✤ Convert Octal (Hexadecimal) to Binary first.

- Regroup the binary number by three bits per group starting from LSB if Octal is required.

- \* Regroup the binary number by four bits per group starting from LSB if Hexadecimal is required.

Octal to Hexadecimal: Convert 26508 to Hexadecimal.

| Octal                           | Hexadecimal                             |

|---------------------------------|-----------------------------------------|

| = 2650                          |                                         |

| = <b>010</b> 110 <b>101</b> 000 | = <b>0101</b> 1010 <b>1000</b> (Binary) |

| Result                          | =(5A8) <sub>16</sub>                    |

*Hexadecimal to octal: Convert* (5A8)<sub>16</sub>*Hexadecimal to Octal.*

| Hexadecimal         | Octal                                    |

|---------------------|------------------------------------------|

| (5A8) <sub>16</sub> | = <b>0101</b> 1010 <b>1000</b> (Binary)  |

|                     | = <b>010</b> 110 <b>101</b> 000 (Binary) |

| Result              | = 2650 (Octal)                           |

\*\*\*\*\*\*\*

# 1's and 2's complement:

## **\*** Explain about 1's and 2's complement with an example.

- Complements are used in digital computers to simplify the subtraction operation and for logical manipulation.

- There are TWO types of complements for each base-r system: the radix complement and the diminished radix complement.

- The first is referred to as the r's complement and the second as the (r -1)'s complement, when the value of the base r is substituted in the name.

- ✤ The two types are referred to as the 2's complement and 1's complement for binary numbers and the 10's complement and 9's complement for decimal numbers.

## Note:

- The 1's complement of a binary number is the number that results when we change all 1's to zeros and the zeros to ones.

- The 2's complement is the binary number that results when we add 1 to the 1's complement.

- It is used to represent negative numbers.

## 2's complement=1's complement+1

| Example 1)<br>Sol: | 1                                 | nber                    |

|--------------------|-----------------------------------|-------------------------|

| Example 2)<br>Sol: | : Find 1's compler<br>1 0 0 1 nur | ment of $(1001)_2$ nber |

$\begin{array}{c} 0 \ 1 \ 1 \ 0 \\ + \ 1 \end{array} \quad 1's \text{ complement} \\ \end{array}$

0111

# Diminished Radix Complement:

Given a number N in base r having n digits, the (r-1)'s complement of N, i.e., its diminished radix complement, is defined as  $(r^n-1) - N$ .

The 9's complement of 546700 is 999999 - 546700 = 453299.

The 9's complement of 012398 is 999999 - 012398 = 987601.

#### Radix Complement:

The *r*'s complement of an *n*-digit number *N* in base *r* is defined as  $r^n - N$  for  $N \neq 0$  and as 0 for N = 0.

For examples:

| The 10's complement of | 012398 | is | 987602 |

|------------------------|--------|----|--------|

| The 10's complement of | 246700 | is | 753300 |

#### Model 1:

Using 10's complement, subtract 72532 - 3250.

| M =                          | 72532         |

|------------------------------|---------------|

| 10's complement of $N = +$   | 96750         |

| Sum =                        | 169282        |

| Discard end carry $10^5 = -$ | <u>100000</u> |

| Answer =                     | 69282         |

(May 2010)

Model 2:

Using 10's complement, subtract 3250 – 72532.

$$M = 03250$$

10's complement of  $N = + \frac{27468}{30718}$

Sum = 30718

#### Model 3:

Given the two binary numbers X = 1010100 and Y = 1000011, perform the subtraction (a) X - Y and (b) Y - X by using 2's complements.

(a)

$$X = 1010100$$

2's complement of  $Y = + 0111101$

Sum = 10010001

Discard end carry  $2^7 = -10000000$

Answer:  $X - Y = 0010001$

(b)  $Y = 1000011$

2's complement of  $X = 0101100$

Sum = 1101111

There is no end carry. Therefore, the answer is Y - X = -(2's complement of 1101111) = -0010001.

# Model 4:

Given the two binary numbers X=1010100 and Y=1000011, perform the subtraction (a) X-Y and (b) Y-X by using 1's complements.

(a)

$$X - Y = 1010100 - 1000011$$

$X = 1010100$

1's complement of  $Y = + 0111100$

Sum = 10010000

Endaround carry = + \_\_\_\_\_1

Answer:  $X - Y = 0010001$

(b)  $Y - X = 1000011 - 1010100$

$Y = 1000011$

1's complement of  $X = + 0101011$

Sum = 1101110

There is no end carry. Therefore, the answer is Y - X = -(1's complement of 1101110) = -0010001.

\*\*\*\*\*

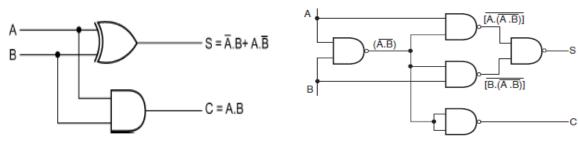

## **ARITHMETIC OPERATIONS**

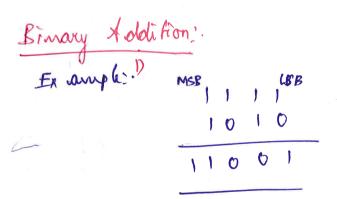

## **Binary** Addition:

## **Rules of Binary Addition**

- 0 + 0 = 0

- 0 + 1 = 1

- 1+0=1

- 1 + 1 = 0, and carry 1 to the next more significant bit

Example:

## Add: 00011010 + 00001100 = 00100110

|     |   | 1 | 1 |   |   |   |   |

|-----|---|---|---|---|---|---|---|

| 0   | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| + 0 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |

| 0   | 0 | 1 | 0 | 0 | 1 | 1 | 0 |

# **Binary** Subtraction:

# **Rules of Binary Subtraction**

- 0 0 = 0•

- 0 1 = 1, and borrow 1 from the next more significant bit •

- 1 0 = 1•

- 1 1 = 0•

# **Example:**

| Sub: | 00100101 - 00010001 = 00010100 |   |   |   |   |   |   |   |

|------|--------------------------------|---|---|---|---|---|---|---|

|      | 0                              | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

|      | - 0                            | 0 | 0 | 1 | 0 | 0 | 0 | 1 |

|      |                                |   |   |   |   |   |   |   |

|      | 0                              | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

|      |                                |   |   |   |   |   |   |   |

# **Binary Multiplication:**

# **Rules of Binary Multiplication**

1

1.

0

- $0 \ge 0 = 0$ •

- $0 \ge 1 = 0$ ٠

- $1 \ge 0 = 0$ •

- $1 \ge 1$ , and no carry or borrow bits •

## Exampl

| (a)        | 0111    | × 1101  |   |            |    |   |   |   |               |

|------------|---------|---------|---|------------|----|---|---|---|---------------|

|            |         |         |   | 0          | 1  | 1 | 1 |   | Multiplicand  |

|            |         |         | × | 1          | 1  | 0 | 1 |   | Multiplier    |

|            |         |         |   | 0          | 1  | 1 | 1 |   |               |

|            |         |         | 0 | 0          | 0  | 0 |   |   | Partial       |

|            |         | 0       | 1 | 1          | 1  |   |   |   | Products      |

|            | 0       | 1       | 1 | 1          |    |   |   |   |               |

|            | 1       | 0       | 1 | 1          | 0  | 1 | 1 |   | Final Product |

| <i>(b)</i> | 1.011 > | × 10.01 |   |            |    |   |   |   |               |

|            |         |         |   | 1.         | 0  | 1 |   | 1 | Multiplican   |

|            |         |         |   | $\times 1$ | 0. | 0 |   | 1 | Multiplier    |

|            |         |         |   | 1          | 0  | 1 |   | 1 |               |

|            |         |         | 0 | 0          | 0  | 0 |   |   | Partial       |

|            |         |         | 0 | 0          | 0  |   |   |   | Products      |

|            |         | 0       | 0 | 0          | 0  |   |   |   | Froducts      |

0

0

1

1

**Final Product**

# **Binary Division:**

Binary division is the repeated process of subtraction, just as in decimal division.

**Example :** (*a*) 11001 ÷ 101

|     |         |      |   | 1 | 0 | 1  |   |   |   |

|-----|---------|------|---|---|---|----|---|---|---|

|     | 1       | 0    | 1 | 1 | 1 | 0  | 0 | 1 | _ |

|     |         |      |   | 1 | 0 | 1  |   |   |   |

|     |         |      |   | 0 | 0 | 1  | 0 | 1 |   |

|     |         |      |   |   |   | 1  | 0 | 1 |   |

|     |         |      |   |   |   | 0  | 0 | 0 |   |

| (b) | 11110 ÷ | 1001 |   |   |   |    |   |   |   |

|     |         |      |   |   | 1 | 1. | 0 | 1 | 0 |

| 1   | 0       | 0    | 1 | 1 | 1 | 1  | 1 | 0 |   |

|     |         |      |   |   | 1 | 0  | 0 | 1 |   |

|     |         |      |   | 0 | 1 | 1  | 0 | 0 |   |

|     |         |      |   |   | 1 | 0  | 0 | 1 |   |

|     |         |      |   |   | 1 | 0  | 0 | 0 | 0 |

|     |         |      |   |   |   | 1  | 0 | 0 | 1 |

|     |         |      |   |   |   |    | 1 | 1 | 0 |

|     |         |      |   |   |   | 1  | 0 | 0 | 1 |

|     |         |      |   |   |   |    | 1 | 0 | 1 |

\*\*\*\*\*

# CODES

# Explain the various codes used in digital systems with an example.

- In digital systems a variety of codes are used to serve different purposes, such as data entry, arithmetic operation, error detection and correction, etc.

- > Selection of a particular code depends on the requirement.

- Codes can be broadly classified into five groups.

- (i) Weighted Binary Codes

- (ii) Non-weighted Codes

- (iii) Error-detection Codes

- (iv) Error-correcting Codes

- (v) Alphanumeric Codes

# Weighted Binary Codes

If each position of a number represents a specific weight then the coding scheme is called weighted binary code.

# BCD Code or 8421 Code:

- > The full form of BCD is 'Binary-Coded Decimal'. Since this is a coding scheme relating decimal and binary numbers, *four bits are required* to code each decimal number.

- For example,  $(35)_{10}$  is represented as 0011 0101 using BCD code, rather than  $(100011)_2$

- Example: Give the BCD equivalent for the decimal number 589.

| The decimal number is              | 5        | 8    | 9    |

|------------------------------------|----------|------|------|

| BCD code is                        | 0101     | 1000 | 1001 |

| Hence, $(589)_{10} = (01011)^{-1}$ | 0001001) | BCD  |      |

# 2421 Code:

- Another weighted code is 2421 code. The weights assigned to the four digits are 2, 4, 2, and 1.

- > The 2421 code is the same as that in BCD from 0 to 4. However, it varies from 5 to 9.

- For example, in this case the bit combination 0100 represents decimal 4; whereas the bit combination 1101 is interpreted as the decimal 7, as obtained from  $2 \times 1 + 1 \times 4 + 0 \times 2 + 1 \times 1 = 7$ .

- > This is also a self-complementary code.

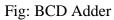

# BCD Addition:

Examples:

> Consider the addition of 184 + 576 = 760 in BCD:

| BCD        | 1     | 1     |      |      |

|------------|-------|-------|------|------|

|            | 0001  | 1000  | 0100 | 184  |

|            | +0101 | 0111  | 0110 | +576 |

| Binary sum | 0111  | 10000 | 1010 |      |

| Add 6      |       | 0110  | 0110 |      |

| BCD sum    | 0111  | 0110  | 0000 | 760  |

> Add the following BCD numbers: (a) 1001 and 0100, (b) 00011001 and 00010100

| Solution                                                                                                                                                                |                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| (a) $1 0 0 1$<br>+ 0 1 0 0                                                                                                                                              |                                        |

| $1  1  0  1  \rightarrow \text{Invalid BCD number}$                                                                                                                     | 9 - 19 - 19 - 19 - 19 - 19 - 19 - 19 - |

| $\begin{array}{c} +0 & 1 & 1 & 0 \\ \hline 1 & 0 & 0 & 1 \\ \hline 1 & 0 & 0 & 0 \end{array} \rightarrow \text{Add } 6 \end{array}$                                     | +4                                     |

| $\underbrace{\begin{array}{ccc} 0 & 0 & 1 \\ 1 & & \\ 1 & & \\ 1 & & \\ 3 & & \\ 3 & & \\ \end{array}}_{3} \rightarrow \text{Valid BCD number}$                         | 13 <sub>10</sub>                       |

| (b) 0 0 0 1 1 0 0 1                                                                                                                                                     |                                        |

| +0 0 0 1 0 1 0 0                                                                                                                                                        |                                        |

| $0$ $0$ $1$ $0$ $1$ $1$ $0$ $1 \rightarrow$ Right group is invalid                                                                                                      | 19                                     |

| $+0$     $0 \rightarrow \text{Add } 6$                                                                                                                                  | +14                                    |

| $\underbrace{\begin{array}{ccc} 0 & 1 & 1 \\ 3 \end{array}}_{3} \underbrace{\begin{array}{ccc} 0 & 0 & 1 & 1 \\ 3 \end{array}}_{3} \rightarrow \text{Valid BCD number}$ | 33,                                    |

|                  | /           |      | 2        |              |   |

|------------------|-------------|------|----------|--------------|---|

| Decimal<br>Digit | BCD<br>8421 | 2421 | Excess-3 | 8, 4, -2, -1 |   |

| 0                | 0000        | 0000 | 0011     | 0000         |   |

| 1                | 0001        | 0001 | 0100     | 0111         |   |

| 2                | 0010        | 0010 | 0101     | 0110         |   |

| 3                | 0011        | 0011 | 0110     | 0101         |   |

| 4                | 0100        | 0100 | 0111     | 0100         |   |

| 5                | 0101        | 1011 | 1000     | 1011         |   |

| 6                | 0110        | 1100 | 1001     | 1010         |   |

| 7                | 0111        | 1101 | 1010     | 1001         |   |

| 8                | 1000        | 1110 | 1011     | 1000         |   |

| 9                | 1001        | 1111 | 1100     | 1111         |   |

|                  | 1010        | 0101 | 0000     | 0001         |   |

| Unused           | 1011        | 0110 | 0001     | 0010         |   |

| bit              | 1100        | 0111 | 0010     | 0011         |   |

| combi-           | 1101        | 1000 | 1101     | 1100         |   |

| nations          | 1110        | 1001 | 1110     | 1101         |   |

|                  | 1111        | 1010 | 1111     | 1110         |   |

|                  |             |      |          |              | ĩ |

Four Different Binary Codes for the Decimal Digits

#### Non-weighted Codes

- ▶ It basically means that each position of the binary number is not assigned a fixed value.

- Excess-3 codes and Gray codes are such non-weighted codes.

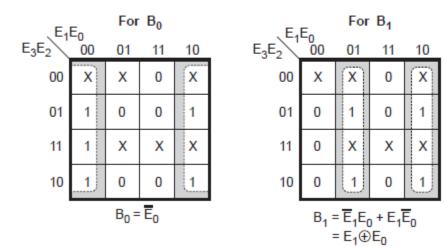

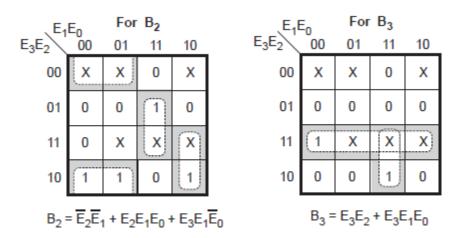

#### Excess-3 code:

- > This code assignment is obtained from the corresponding value of 4-bit binary code after adding 3 to the given decimal digit.

- **Example:** 1000 of 8421 (BCD) = 1011 in Excess-3.

#### [NOV 2020]

| * | Convert (367 | ) <sub>10</sub> into its Excess-3 code. | and    | Decimal       | (643) to  | Excess - 3 code |

|---|--------------|-----------------------------------------|--------|---------------|-----------|-----------------|

|   | Solution.    | The decimal number is                   | 3      | 6             | 7         |                 |

|   |              | Add 3 to each bit                       | +3     | +3            | +3        |                 |

|   |              | Sum                                     | 6      | 9             | 10        |                 |

|   | Co           | nverting the above sum in               | to 4-b | it binary     | equivalen | t, we have a    |

|   | 4-k          | oit binary equivalent of                | 0110   | 1001          | 1010      |                 |

|   | He           | ence, the Excess-3 code for             | (367)1 | $_{0} = 0110$ | 1001 1010 | )               |

|   |              | Excess-3 code f                         | or 64. | 3 = 1001      | 0111 01   | 10              |

## Gray code:

- ▶ Gray code belongs to a class of code known as minimum change code, in which a number changes by only one bit as it proceeds from one number to the next.

- > This code finds use for shift encoders, in some types of analog-to-digital converters, etc.

- > The gray code is a reflective digital code which has the special property that any two subsequent numbers codes differ by only one bit. This is also called a *unit-distance code*.

| Decimal numbers | Binary code | Gray code |

|-----------------|-------------|-----------|

| 0               | 0000        | 0000      |

| 1               | 0001        | 0001      |

| 2               | 0010        | 0011      |

| 3               | 0011        | 0010      |

| 4               | 0100        | 0110      |

| 5               | 0101        | 0111      |

| 6               | 0110        | 0101      |

| 7               | 0111        | 0100      |

| 8               | 1000        | 1100      |

| 9               | 1001        | 1101      |

| 10              | 1010        | 1111      |

| 11              | 1011        | 1110      |

| 12              | 1100        | 1010      |

| 13              | 1101        | 1011      |

| 14              | 1110        | 1001      |

| 15              | 1111        | 1000      |

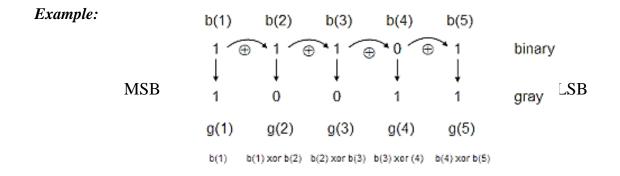

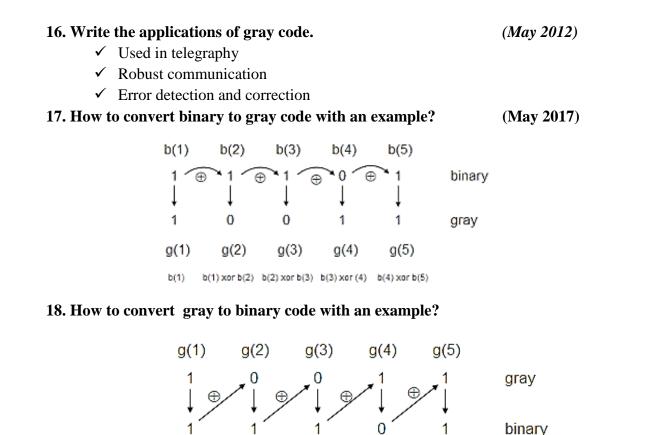

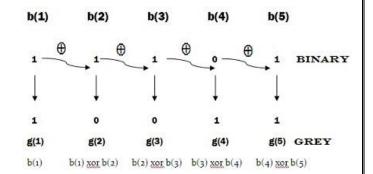

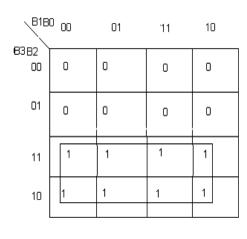

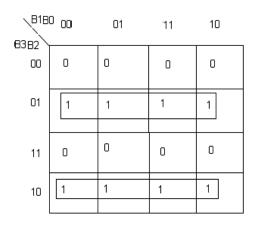

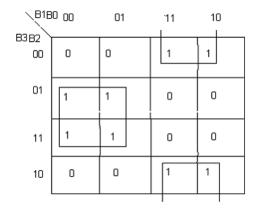

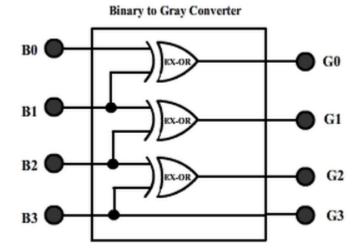

# Binary to Gray Code Conversion:

Any binary number can be converted into equivalent Gray code by the following steps:

- i) the MSB of the Gray code is the same as the MSB of the binary number;

- ii) the second bit next to the MSB of the Gray code equals the Ex-OR of the MSB and second bit of the binary number; it will be 0 if there are same binary bits or it will be 1 for different binary bits;

- iii) the third bit for Gray code equals the exclusive-OR of the second and third bits of the binary number, and similarly all the next lower order bits follow the same mechanism.

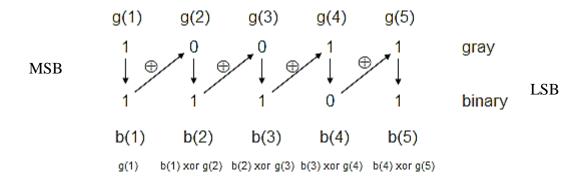

# Gray Code to Binary Code Conversion:

Any Gray code can be converted into an equivalent binary number by the following steps:

- i. The MSB of the binary number is the same as the MSB of the Gray code.

- ii. the second bit next to the MSB of the binary number equals the Ex-OR of the MSB of the binary number and second bit of the Gray code; it will be 0 if there are same binary bits or it will be 1 for different binary bits;

- iii. the third bit for the binary number equals the exclusive-OR of the second bit of the binary number and third bit of the Gray code, and similarly all the next lower order bits follow the same mechanism.

# Example:

## Error detecting codes

- When data is transmitted from one point to another, like in wireless transmission, or it is just stored, like in hard disks and memories, there are chances that data may get corrupted.

- $\blacktriangleright$  To detect these data errors, we use special codes, which are error detection codes.

## Two types of parity

- **Even parity:** Checks if there is an even number of ones; if so, parity bit is zero. When the number of one's is odd then parity bit is set to 1.

- ➤ Odd Parity: Checks if there is an odd number of ones; if so, parity bit is zero. When the number of one's is even then parity bit is set to 1.

# Error correcting code

- > Error-correcting codes not only detect errors, but also correct them.

- This is used normally in Satellite communication, where turn-around delay is very high as is the probability of data getting corrupt.

# Hamming codes

- Hamming code adds a minimum number of bits to the data transmitted in a noisy channel, to be able to correct every possible one-bit error.

- It can detect (not correct) two-bit errors and cannot distinguish between 1-bit and 2-bits inconsistencies. It can't in general detect 3(or more)-bits errors.

## **Alphanumeric Codes**

An alphanumeric code is a binary code of a group of elements consisting of ten decimal digits, the 26 letters of the alphabet (both in uppercase and lowercase), and a certain number of special symbols such as #, /, &, %, etc.

#### ASCII (American Standard Code for Information Interchange)

- ▶ It is actually a 7-bit code, where a character is represented with seven bits.

- > The character is stored as one byte with one bit remaining unused.

- > But often the extra bit is used to extend the ASCII to represent an additional 128 characters.

## EBCDIC codes

- > EBCDIC stands for *Extended Binary Coded Decimal Interchange*.

- It is also an alphanumeric code generally used in IBM equipment and in large computers for communicating alphanumeric data.

- ➢ For the different alphanumeric characters the code grouping in this code is different from the ASCII code. It is actually an 8-bit code and a ninth bit is added as the parity bit.

#### \*\*\*\*\*\*\*\*\*\*

#### **Boolean Algebra and Theorems**

#### Discuss the different postulates of Boolean theorems.

#### **Definition:**

- Boolean algebra is an algebraic structure defined by a set of elements B, together with two binary operators. '+' and '-', provided that the following postulates are satisfied.

- It can be used to simplify many a complex Boolean expression and also to transform the given expression into more useful and meaningful equivalent expression.

#### T1: Commutative Law

| (a) | A + | B = B | +A |

|-----|-----|-------|----|

|     |     |       |    |

(b) A B = B A

T2: Associative Law

(a) (A + B) + C = A + (B + C)

(b) (A B) C = A (B C)

## T3: Distributive Law

(a) A (B + C) = A B + A C(b) A + (B C) = (A + B) (A + C)

## T4: Identity Law

(a) A + A = A

(b) A A = A

T5: Negation Law  $(\overline{A}) = \overline{A}$  and  $(\overline{\overline{A}}) = A$

#### T6: Redundancy

(a) A + A B = A(b) A (A + B) = A

#### T7: Operations with '0' & '1'

- (a)  $\theta + A = A$

- (b) I A = A

- (c) l + A = l

- (d) 0A = 0

- **T8 : Complement laws**

- (a)  $\bar{A} + A = 1$ (b)  $\bar{A} \cdot A = 0$

- **T9:** (a)  $A + \overline{AB} = A + B$ (b) A.  $(\overline{A} + B) = A.B$

# Postulates of Boolean Algebra:

- The postulates of a mathematical system form the basic assumptions from which it is possible to deduce the rules, theorems, and properties of the system.

- > The following are the important postulates of Boolean algebra:

| 1. | 1*1 = 1       | 0+0=0.        |

|----|---------------|---------------|

| 2. | 1*0 = 0*1 = 0 | 0+1 = 1+0 = 1 |

| 3. | 0*0 = 0       | 1 + 1 = 1     |

- 4. 1' = 0 and 0' = 1.

- Many theorems of Boolean algebra are based on these postulates, which can be used to simplify Boolean expressions.

The operators and postulates have the following meanings:

- ✓ The binary operator + defines addition.

- $\checkmark$  The additive identity is 0.

- $\checkmark$  The additive inverse defines subtraction.

- ✓ The binary operator .(dot) defines multiplication.

- $\checkmark$  The multiplicative identity is 1.

- $\checkmark$  The only distributive law applicable is that of .(dot) over +:

$a \cdot (b + c) = (a \cdot b) + (a \cdot c)$

# **Two-Valued Boolean Algebra:**

A two-valued Boolean algebra is defined on a set of two elements,  $B = \{0, 1\}$ , with rules for the two binary operators + and .(dot) as shown in the following operator tables.

| x | y | x·y | x | y | x + y | x | <b>x</b> ′ |

|---|---|-----|---|---|-------|---|------------|

| 0 | 0 | 0   | 0 | 0 | 0     | 0 | 1          |

| 0 | 1 | 0   | 0 | 1 | 1     | 1 | 0          |

| 1 | 0 | 0   | 1 | 0 | 1     |   |            |

| 1 | 1 | 1   | 1 | 1 | 1     |   |            |

# **Duality Principle:**

- The *duality principle* states that every algebraic expression deducible from the postulates of Boolean algebra remains valid if the operators and identity elements are interchanged.

- If the *dual* of an algebraic expression is desired, we simply interchange OR and AND operators and replace 1's by 0's and 0's by 1's.

# De-Morgan's theorem:

- 1. The complement of product is equal to the sum of their complements. (X.Y)'=X'+Y'

- 2. The complement of sum is equal to the product of their complements. (X+Y)' = X'.Y'

# **Basic Theorems:**

Postulates and Theorems of Boolean Algebra

| Postulate 2               | (a) | x + 0 = x                 | (b) | $x \cdot 1 = x$         |

|---------------------------|-----|---------------------------|-----|-------------------------|

| Postulate 5               | (a) | x + x' = 1                | (b) | $x \cdot x' = 0$        |

| Theorem 1                 | (a) | x + x = x                 | (b) | $x \cdot x = x$         |

| Theorem 2                 | (a) | x + 1 = 1                 | (b) | $x \cdot 0 = 0$         |

| Theorem 3, involution     |     | (x')' = x                 |     |                         |

| Postulate 3, commutative  | (a) | x + y = y + x             | (b) | xy = yx                 |

| Theorem 4, associative    | (a) | x + (y + z) = (x + y) + z | (b) | x(yz) = (xy)z           |

| Postulate 4, distributive | (a) | x(y+z) = xy + xz          | (b) | x + yz = (x + y)(x + z) |

| Theorem 5, DeMorgan       | (a) | (x + y)' = x'y'           | (b) | (xy)' = x' + y'         |

| Theorem 6, absorption     | (a) | x + xy = x                | (b) | x(x + y) = x            |

THEOREM 1(a): x + x = x.

| Statement                 | Justification  |

|---------------------------|----------------|

| $x + x = (x + x) \cdot 1$ | postulate 2(b) |

| = (x+x)(x+x')             | 5(a)           |

| = x + xx'                 | 4(b)           |

| = x + 0                   | 5(b)           |

| = x                       | 2(a)           |

THEOREM 1(b):  $x \cdot x = x$ .

| Statement            | Justification  |

|----------------------|----------------|

| $x \cdot x = xx + 0$ | postulate 2(a) |

| = xx + xx'           | 5(b)           |

| =x(x+x')             | 4(a)           |

| $= x \cdot 1$        | 5(a)           |

| = x                  | 2(b)           |

**THEOREM 2(a):** x + 1 = 1.

| Statement                 | Justification  |

|---------------------------|----------------|

| $x + 1 = 1 \cdot (x + 1)$ | postulate 2(b) |

| = (x + x')(x + 1)         | 5(a)           |

| $= x + x' \cdot 1$        | 4(b)           |

| = x + x'                  | 2(b)           |

| = 1                       | 5(a)           |

**THEOREM 2(b):**  $x \cdot 0 = 0$  by duality.

**THEOREM 3:** (x')' = x. From postulate 5, we have x + x' = 1 and  $x \cdot x' = 0$ , which together define the complement of x. The complement of x' is x and is also (x')'.

THEOREM 6(a): x + xy = x.

| Statement                 | Justification  |

|---------------------------|----------------|

| $x + xy = x \cdot 1 + xy$ | postulate 2(b) |

| = x(1 + y)                | 4(a)           |

| = x(y + 1)                | 3(a)           |

| $= x \cdot 1$             | 2(a)           |

| = x                       | 2(b)           |

**THEOREM 6(b):** x(x + y) = x by duality.

\*\*\*\*\*\*

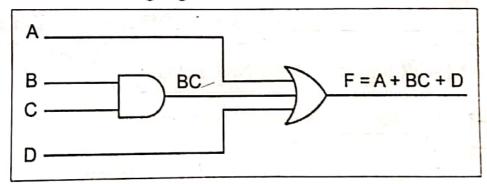

#### **Boolean Functions**

- Boolean algebra is an algebra that deals with binary variables and logic operations.

- A Boolean function described by an algebraic expression consists of binary variables, the constants 0 and 1, and the logic operation symbols.

- For a given value of the binary variables, the function can be equal to either 1 or 0.

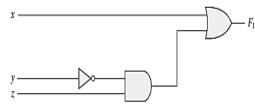

**Example:** Consider the Boolean function, F1 = x + y'z

> The gate implementation of F1 is shown below.

#### **Examples:**

Simplify the following Boolean functions to a minimum number of literals.

1.

$$x(x' + y) = xx' + xy = 0 + xy = xy$$

.

2.

$$x + x'y = (x + x')(x + y) = 1(x + y) = x + y$$

.

3.

$$(x + y)(x + y') = x + xy + xy' + yy' = x(1 + y + y') = x$$

.

4.

$$xy + x'z + yz = xy + x'z + yz(x + x')$$

=  $xy + x'z + xyz + x'yz$

=  $xy(1 + z) + x'z(1 + y)$

=  $xy + x'z$ .

5. (x + y)(x' + z)(y + z) = (x + y)(x' + z), by duality from function 4.

# Complement of a function:

> The complement of a function F is obtained from an interchange of 0's for 1's and 1's for 0's in the value of F.

#### Example: 1. Sin

Simplify:-

$$(A + B + C)' = (A + x)'$$

let  $B + C = x$

$= A'x'$  by theorem 5(a) (DeMorgan)

$= A'(B + C)'$  substitute  $B + C = x$

$= A'(B'C')$  by theorem 5(a) (DeMorgan)

$= A'B'C'$  by theorem 4(b) (associative)

2. Find the complement of the functions F1 = x'yz' + x'y'z and F2 = x(y'z' + yz). Solution:

By applying DeMorgan's theorem, the complements are obtained as follows:

$$F'_{1} = (x'yz' + x'y'z)' = (x'yz')'(x'y'z)' = (x + y' + z)(x + y + z')$$

$$F'_{2} = [x(y'z' + yz)]' = x' + (y'z' + yz)' = x' + (y'z')'(yz)'$$

$$= x' + (y + z)(y' + z')$$

$$= x' + yz' + y'z$$

3. Find the complement of the functions F1 = x'yz' + x'y'z and F2 = x(y'z' + yz) by taking their duals and complementing each literals.

Solution:

- 1.  $F_1 = x'yz' + x'y'z$ . The dual of  $F_1$  is (x' + y + z')(x' + y' + z). Complement each literal:  $(x + y' + z)(x + y + z') = F'_1$ .

- 2.  $F_2 = x(y'z' + yz)$ . The dual of  $F_2$  is x + (y' + z')(y + z). Complement each literal:  $x' + (y + z)(y' + z') = F'_2$ .

\*\*\*\*\*

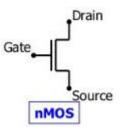

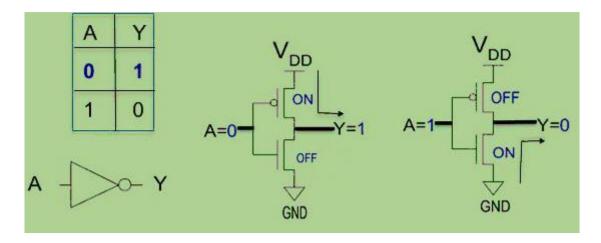

# LOGIC GATES

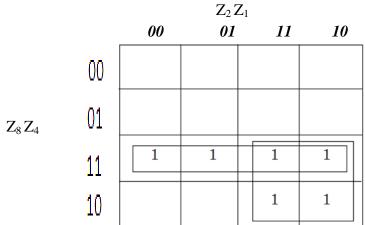

## Discuss the various logic gates with its truth table.

- ◆ A logic gate is an idealized or physical device implementing a Boolean function.

- It performs a logical operation on one or more logical inputs, and produces a single logical output.

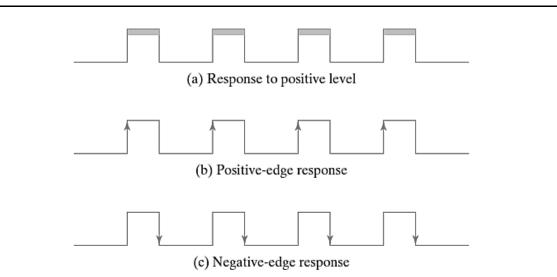

# Positive and Negative Logic:

- ◆ The binary variables have two states, i.e. the logic '0' state or the logic '1' state.

- These are represented by two different voltage levels or two different current levels.

- If the more positive of the two voltage or current levels represents a logic '1' and the less positive of the two levels represents a logic '0', then the logic system is referred to as a *positive logic system*.

- If the more positive of the two voltage or current levels represents a logic '0' and the less positive of the two levels represents a logic '1', then the logic system is referred to as a *negative logic system*.

## Truth Table

A truth table lists all possible combinations of input binary variables and the corresponding outputs of a logic system.

| Name                               | Graphic<br>symbol       | Algebraic<br>function             | Truth<br>table                                                                                          |

|------------------------------------|-------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------|

| AND                                | x                       | $F = x \cdot y$                   | x y F<br>0 0 0<br>0 1 0<br>1 0 0<br>1 1 1                                                               |

| OR                                 | x<br>y                  | F = x + y                         | x y F<br>0 0 0<br>0 1 1<br>1 0 1<br>1 1 1                                                               |

| Inverter                           | x>oF                    | F = x'                            | x F<br>0 1<br>1 0                                                                                       |

| Buffer                             | x                       | F = x                             | x F<br>0 0<br>1 1                                                                                       |

| NAND                               | xp                      | F = (xy)'                         | $\begin{array}{c ccc} x & y & F \\ \hline 0 & 0 & 1 \\ 0 & 1 & 1 \\ 1 & 0 & 1 \\ 1 & 1 & 0 \end{array}$ |

| NOR                                | x                       | F = (x + y)'                      | x y F<br>0 0 1<br>0 1 0<br>1 0 0<br>1 1 0                                                               |

| Exclusive-OR<br>(XOR)              | \$, <b>₩</b> , <b>₽</b> | $F = xy' + x'y$ $= x \oplus y$    | x y F<br>0 0 0<br>0 1 1<br>1 0 1<br>1 1 0                                                               |

| Exclusive-NOR<br>or<br>equivalence | \$, <b>₩</b> , <b>₽</b> | $F = xy + x'y'$ $= (x \oplus y)'$ | x y F<br>0 0 1<br>0 1 0<br>1 0 0<br>1 1 1                                                               |

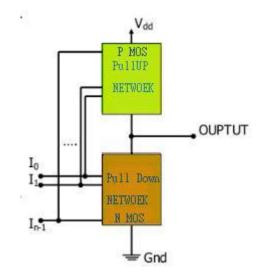

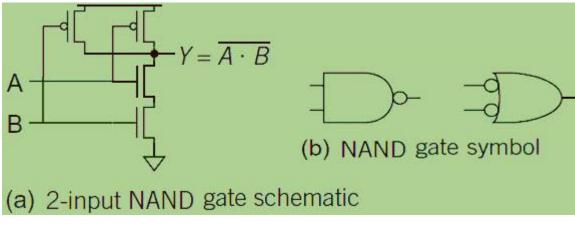

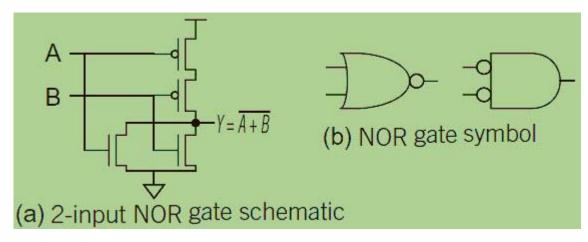

## Universal Gates(NAND & NOR)

- The OR, AND and NOT gates are the three basic logic gates, It can be used to construct the logic circuit for any given Boolean expression.

- The NOR and NAND gate have the property that they individually can be used to hardwareimplement a logic circuit corresponding to any given Boolean expression.

- It is possible to use either only NAND gates or only NOR gates to implement any Boolean expression.

- This is so because a combination of NAND gates or a combination of NOR gates can be used to perform functions of any of the basic logic gates.

- ✤ It is for this reason that NAND and NOR gates are universal gates.

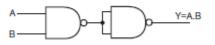

Implementation of basic gates using NAND gate:

Inverter (NOT gate):

AND gate:

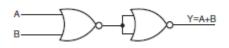

OR gate:

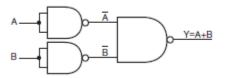

Implementation of basic gates using NOR gate:

Inverter (NOT gate):

AND gate:

**OR gate:**

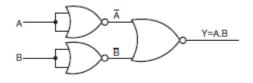

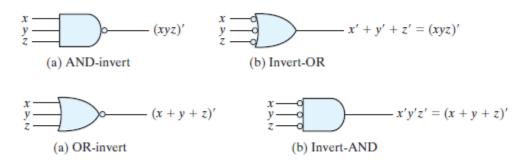

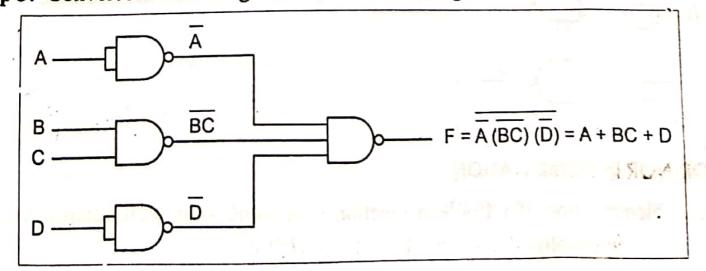

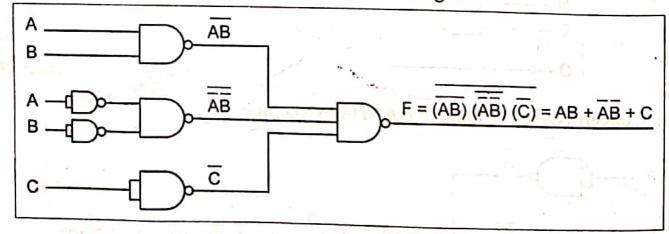

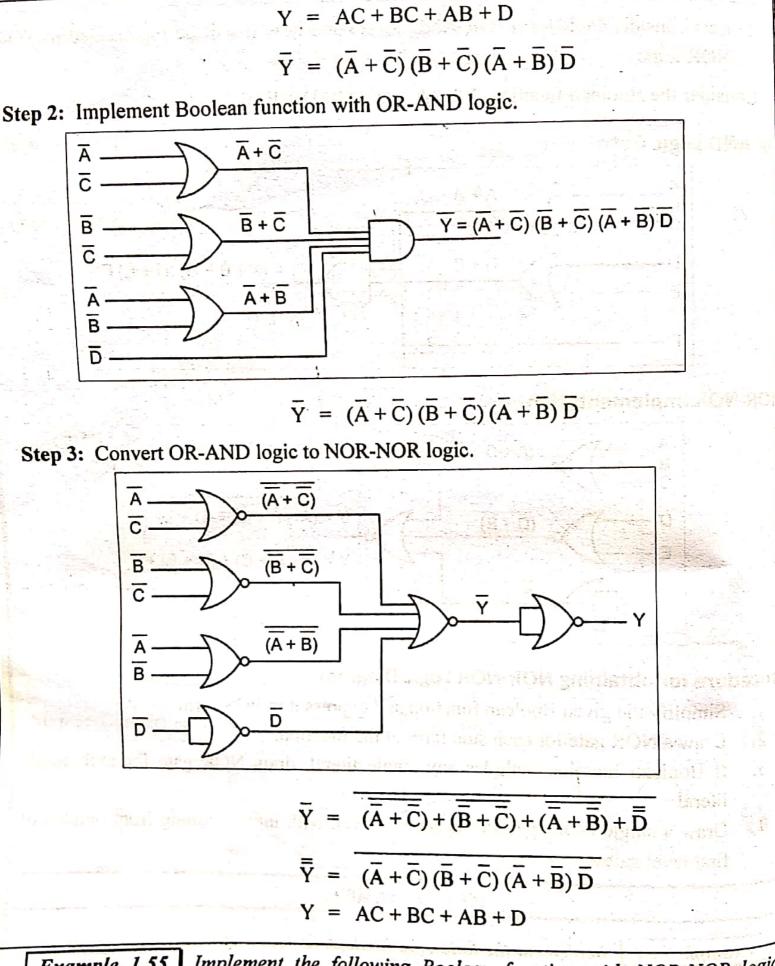

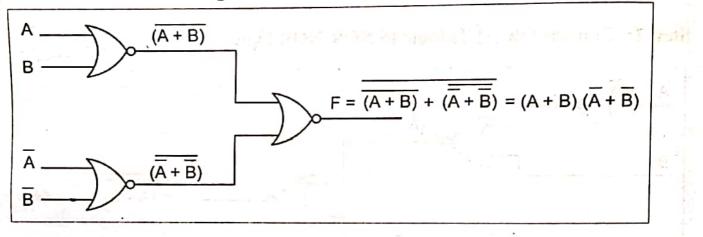

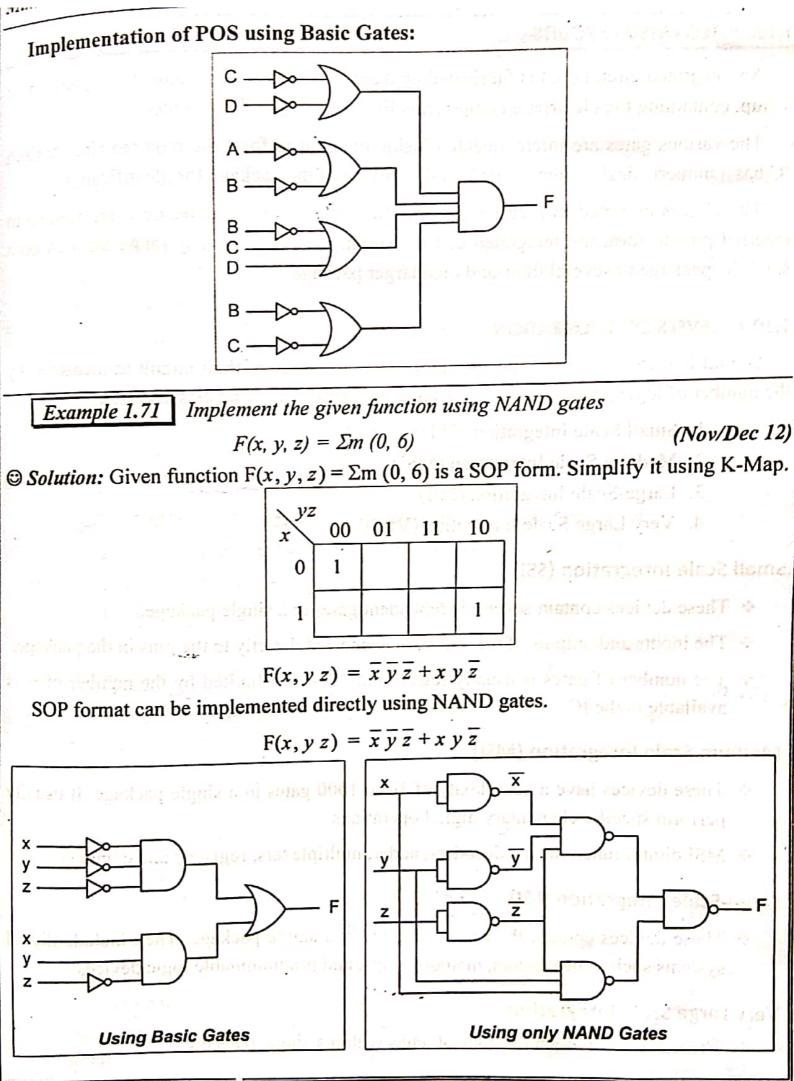

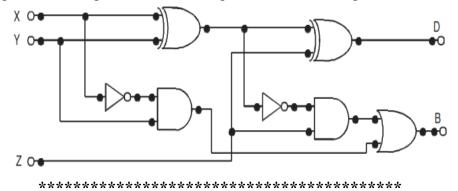

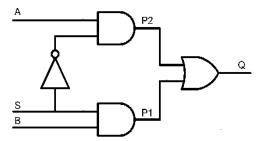

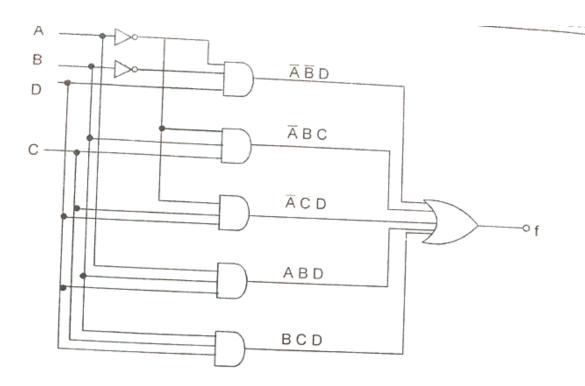

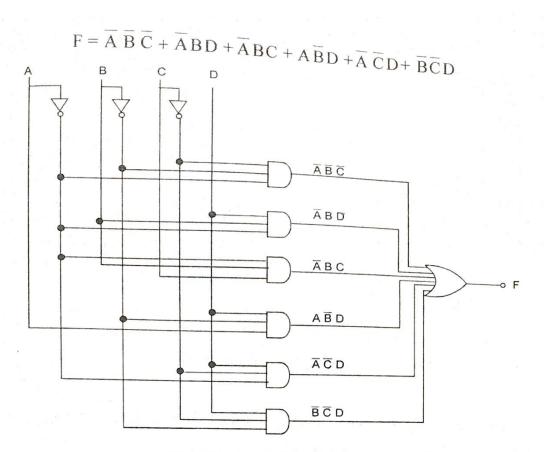

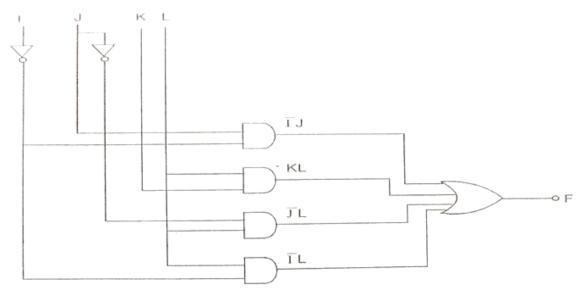

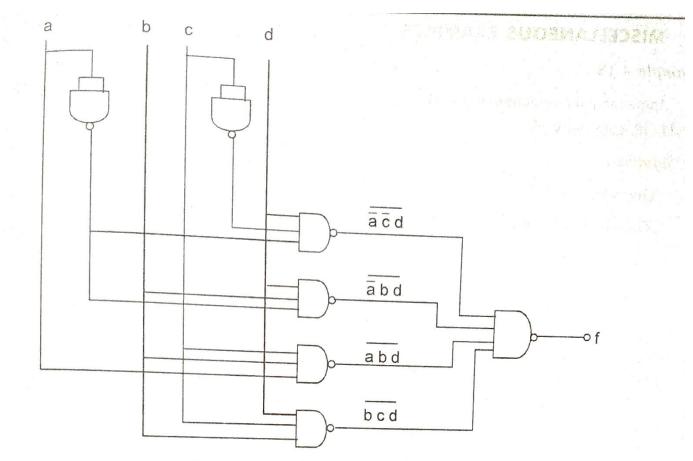

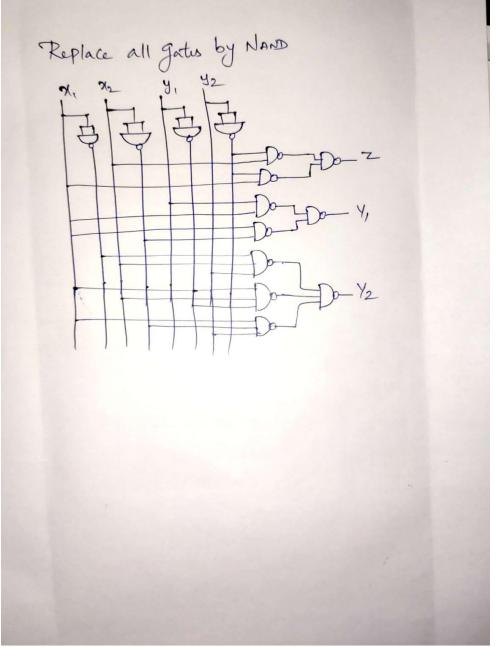

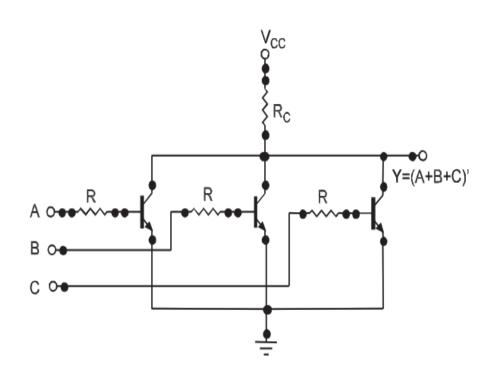

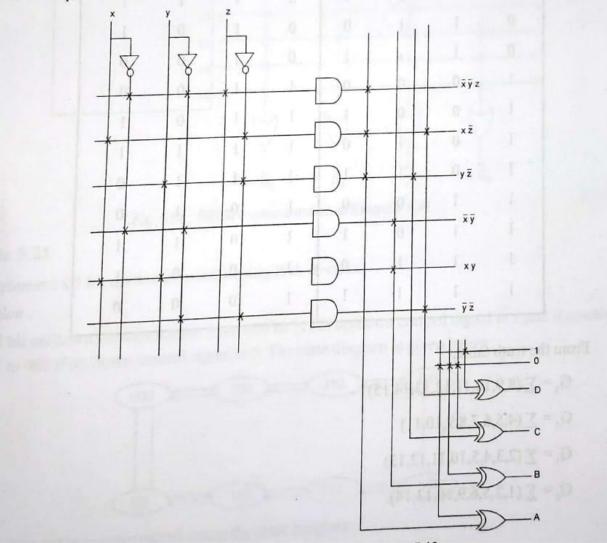

# NAND–NOR implementations:

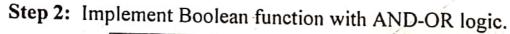

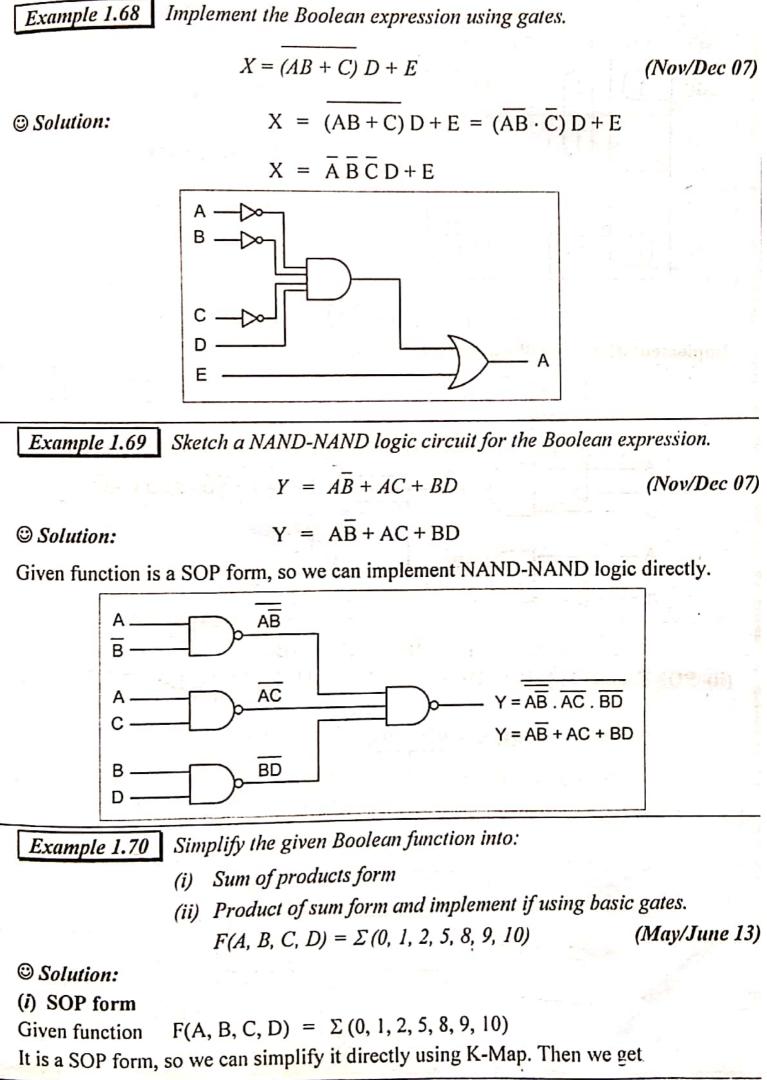

- Digital circuits are frequently constructed with NAND or NOR gates rather than with AND and OR gates.

- NAND and NOR gates are easier to fabricate with electronic components and are the basic gates used in all IC digital logic families.

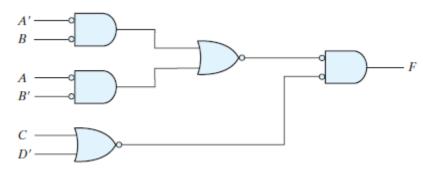

- Because of the prominence of NAND and NOR gates in the design of digital circuits, rules and procedures have been developed for the conversion from Boolean functions given in terms of AND, OR, and NOT into equivalent NAND and NOR logic diagrams.

# Only NAND/NOR gate circuit:

- A convenient way to implement a Boolean function with NAND/NOR gates is to obtain the simplified Boolean function in terms of Boolean operators and then convert the function to NAND/NOR logic.

- The conversion of an algebraic expression from AND, OR, and complement to NAND/NOR can be done by simple circuit manipulation techniques that change AND–OR diagrams to NAND/NOR diagrams.

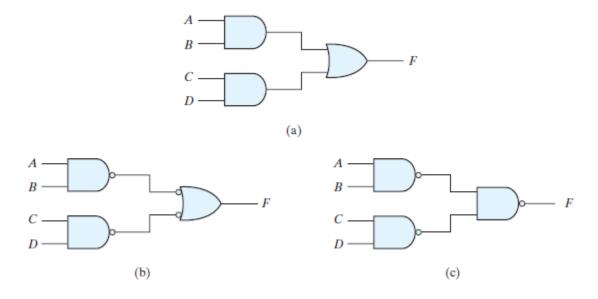

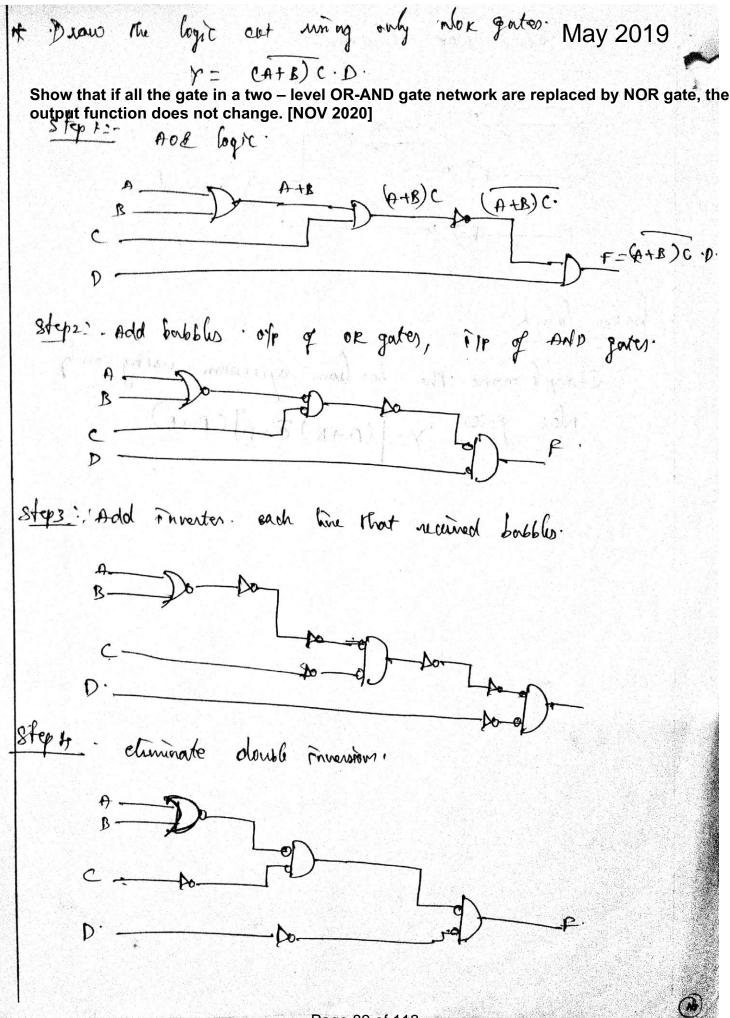

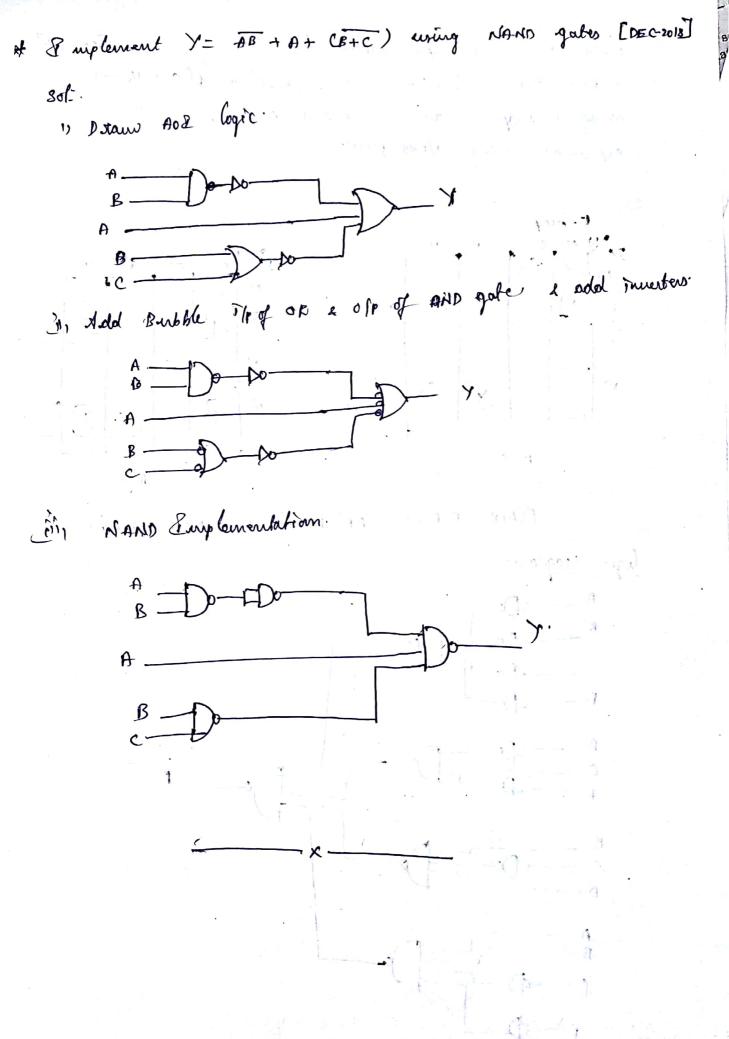

# NAND Implementation Procedure:

- ✓ Draw the AOI logic of given Boolean expression.

- $\checkmark$  Add bubble on input of OR gate & output of AND gate.

- $\checkmark$  Add an Inverter on each line that received bubbles.

- ✓ Eliminate double inversions

- ✓ Replace all by NAND gates

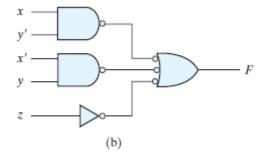

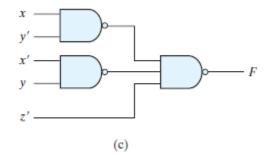

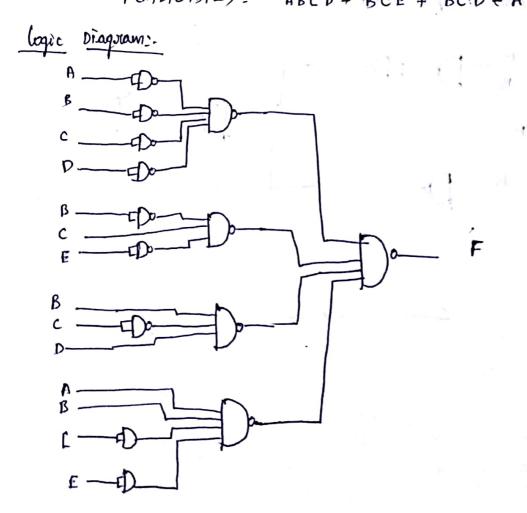

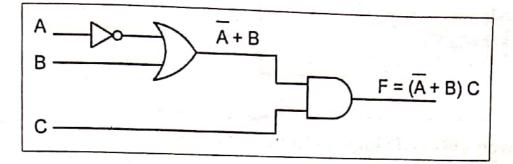

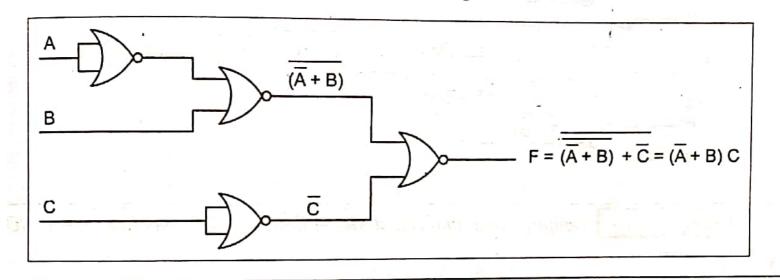

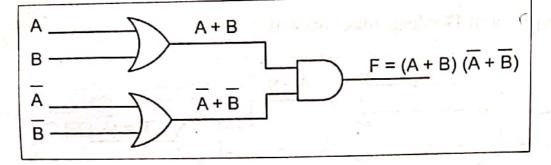

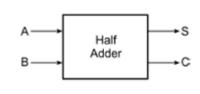

Example:

1. Implement F = AB + CD using only NAND gate.

2. Implement the following Boolean function with NAND gates: F(x, y, z) = (1, 2, 3, 4, 5, 7)

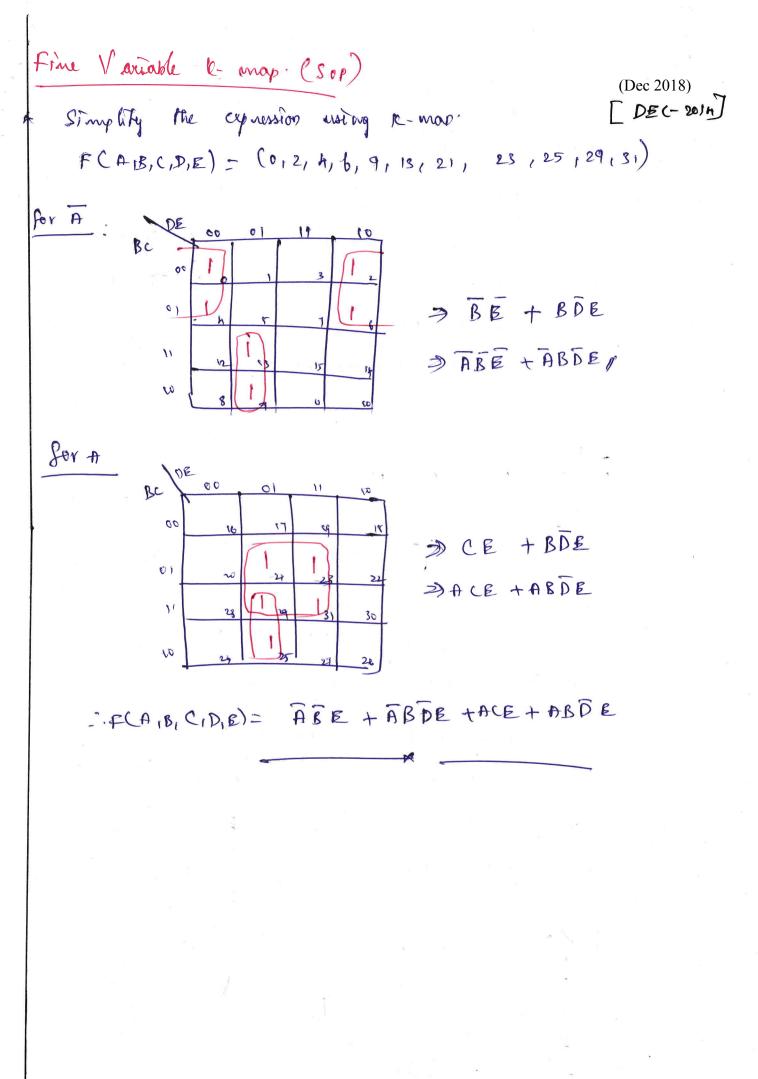

(Dec 2018) (Dec 2014)

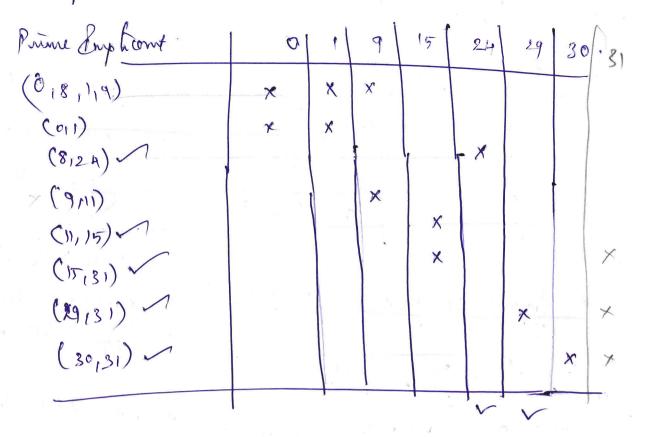

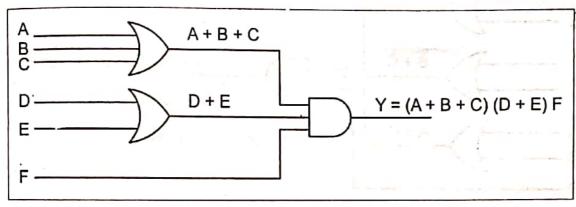

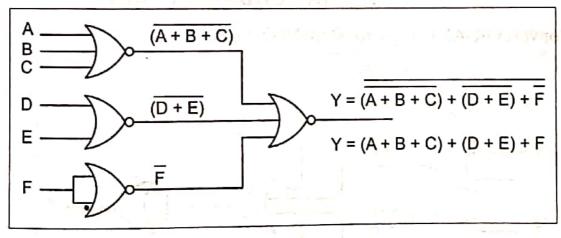

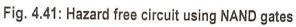

# **NOR Implementation Procedure:**

- $\checkmark$  Draw the AOI logic of given Boolean expression.

- $\checkmark$  Add bubble on input of AND gate & output of OR gate.

- $\checkmark$  Add an Inverter on each line that received bubbles.

- ✓ Eliminate double inversions

- ✓ Replace all by NOR gates

# Example:

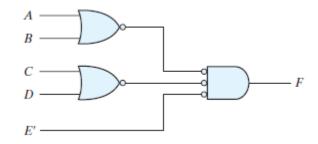

1. Implement F = (A + B)(C + D)E using only NOR gate.

2. Implement F = (AB' + A'B)(C + D') using only NOR gate.

\*\*\*\*\*

# CANONICAL AND STANDARD FORMS

# Explain canonical SOP & POS form with suitable example.

- Binary logic values obtained by the logical functions and logic variables are in binary form. An arbitrary logic function can be expressed in the following forms.

- (i) Sum of the Products (SOP)

- (ii) Product of the Sums (POS)

- Boolean functions expressed as a sum of minterms or product of maxterms are said to be in canonical form.

## **Product term:**

The AND function is referred to as a product. The variable in a product term can appear either in complementary or uncomplimentary form. Example: ABC'

## Sum term:

The OR function is referred to as a Sum. The variable in a sum term can appear either in complementary or uncomplimentary form. Example: A+B+C'

# **Sum of Product (SOP):**

The logical sum of two or more logical product terms is called sum of product expression. It is basically an OR operation of AND operated variables. Example: Y=AB+BC+CA

# **Product of Sum (POS):**

The logical product of two or more logical sum terms is called product of sum expression. It is basically an AND operation of OR operated variables. Example: Y=(A+B).(B+C).(C+A)

# Minterm:

A product term containing all the K variables of the function in either complementary or uncomplimentary form is called Minterm or standard product.

## Maxterm:

➤ A sum term containing all the K variables of the function in either complementary or uncomplimentary form is called Maxterm or standard sum.

|   |   |   | Minterms |                | Maxte        | erms        |

|---|---|---|----------|----------------|--------------|-------------|

| x | y | z | Term     | Designation    | Term         | Designation |

| 0 | 0 | 0 | x'y'z'   | $m_0$          | x + y + z    | $M_0$       |

| 0 | 0 | 1 | x'y'z    | $m_1$          | x + y + z'   | $M_1$       |

| 0 | 1 | 0 | x'yz'    | $m_2$          | x + y' + z   | $M_2$       |

| 0 | 1 | 1 | x'yz     | $m_3$          | x + y' + z'  | $M_3$       |

| 1 | 0 | 0 | xy'z'    | $m_4$          | x' + y + z   | $M_4$       |

| 1 | 0 | 1 | xy'z     | $m_5$          | x' + y + z'  | $M_5$       |

| 1 | 1 | 0 | xyz'     | m <sub>6</sub> | x' + y' + z  | $M_6$       |

| 1 | 1 | 1 | xyz      | $m_7$          | x' + y' + z' | $M_7$       |

Minterms and Maxterms for Three Binary Variables

# **Canonical SOP Expression:**

The minterms whose sum defines the Boolean function are those which give the 1's of the function in a truth table.

# Procedure for obtaining Canonical SOP expression:

- ✓ Examine each term in a given logic function. Retain if it is a minterm, continue to examine the next term in the same manner.

- ✓ Check for the variables that are missing in each product which is not minterm. Multiply the product by (X+X'), for each variable X that is missing.

- $\checkmark$  Multiply all the products and omit the redundant terms.

# Example 1:

# Express the Boolean function F = A + B'C as a sum of minterms. (Dec 2017)

# Solution:

The function has three variables: *A*, *B*, and *C*.

The first term A is missing two variables; therefore,

A = A(B + B') = AB + AB'

This function is still missing one variable, so

A = AB(C + C') + AB'(C + C')

= ABC + ABC' + AB'C + AB'C'

The second term B'C is missing one variable; hence,

B'C = B'C(A + A') = AB'C + A'B'C

Combining all terms, we have

F = A + B'C = ABC + ABC' + AB'C + AB'C' + A'B'C

But AB'C appears twice, and according to theorem 1 (x + x = x), it is possible to remove one of those occurrences.

Rearranging the minterms in ascending order, we finally obtain

F = A'B'C + AB'C + AB'C + ABC' + ABC= m1 + m4 + m5 + m6 + m7  $F(A, B, C) = \sum (1, 4, 5, 6, 7)$

# Example 2: Obtain the canonical sum of product form of the following function. (May 2014)

[NOV 2020]

F (A, B, C) = A + BC = A (B + B') (C + C') + BC (A + A') = (AB + AB') (C + C') + ABC + A'BC = ABC + AB'C + ABC' + AB'C' + ABC + A'BC = ABC + AB'C + ABC' + AB'C' + A'BC (as ABC + ABC = ABC)Hence the canonical sum of the product expression of the given function is

F (A, B) = ABC + AB'C + ABC' + AB'C' + A'BC.

# POS Form: F = (A'+B'+C')(A'+B+C')(A'+B'+C)(A'+B+C)(A+B'+C')

#### **Canonical POS Expression:**

The Maxterms whose product defines the Boolean function are those which give the 1's of the function in a truth table.

#### **Procedure for obtaining Canonical POS expression:**

- ✓ Examine each term in a given logic function. Retain if it is a maxterm, continue to examine the next term in the same manner.

- ✓ Check for the variables that are missing in each sum which is not maxterm. Add (X.X'), for each variable X that is missing.

- $\checkmark$  Expand the expression using distributive property eliminate the redundant terms.

#### Example1:

## Express the Boolean function F = xy + x'z as a product of maxterms.

#### Solution:

First, convert the function into OR terms by using the distributive law:

$F = xy + x_z = (xy + x')(xy + z)$ = (x + x')(y + x')(x + z)(y + z)

= (x' + y)(x + z)(y + z)

The function has three variables: x, y, and z. Each OR term is missing one variable;

#### therefore,

$x'+y = x' + y + z \cdot z' = (x' + y + z)(x' + y + z')$   $x + z = x + z + y \cdot y' = (x + y + z)(x + y' + z)$  $y + z = y + z + x \cdot x' = (x + y + z)(x' + y + z)$

Combining all the terms and removing those which appear more than once, we finally obtain  $F = (x + y + z)(x + y - z)(x_{-} + y + z)(x_{-} + y + z_{-}) = M0.M2.M4.M5$  $F(x, y, z) = \pi(0, 2, 4, 5)$

#### Example 2:

Obtain the canonical product of the sum form of the following function.F(A, B, C) = (A + B') (B + C) (A + C')(Dec 2012)

Solution:

$\begin{array}{l} {\rm F}\ ({\rm A},\ {\rm B},\ {\rm C}) = ({\rm A}+{\rm B}')\ ({\rm B}+{\rm C})\ ({\rm A}+{\rm C}') \\ = ({\rm A}+{\rm B}'+0)\ ({\rm B}+{\rm C}+0)\ ({\rm A}+{\rm C}'+0) \\ = ({\rm A}+{\rm B}'+{\rm CC}')\ ({\rm B}+{\rm C}+{\rm AA}')\ ({\rm A}+{\rm C}'+{\rm BB}') \\ = ({\rm A}+{\rm B}'+{\rm C})\ ({\rm A}+{\rm B}'+{\rm C}')\ ({\rm A}+{\rm B}+{\rm C})\ ({\rm A}'+{\rm B}+{\rm C})\ ({\rm A}+{\rm B}+{\rm C}') \\ ({\rm A}+{\rm B}'+{\rm C}') \\ [{\rm using the distributive property, as X+YZ = (X+Y)(X+Z)] \\ = ({\rm A}+{\rm B}'+{\rm C})\ ({\rm A}+{\rm B}'+{\rm C}')\ ({\rm A}+{\rm B}+{\rm C})\ ({\rm A}'+{\rm B}+{\rm C})\ ({\rm A}+{\rm B}+{\rm C}') \\ [{\rm as }\ ({\rm A}+{\rm B}'+{\rm C}')\ ({\rm A}+{\rm B}'+{\rm C}') = {\rm A}+{\rm B}'+{\rm C}'] \\ \end{array}$

#### \*\*\*\*\*

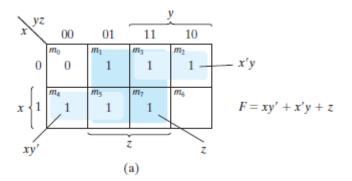

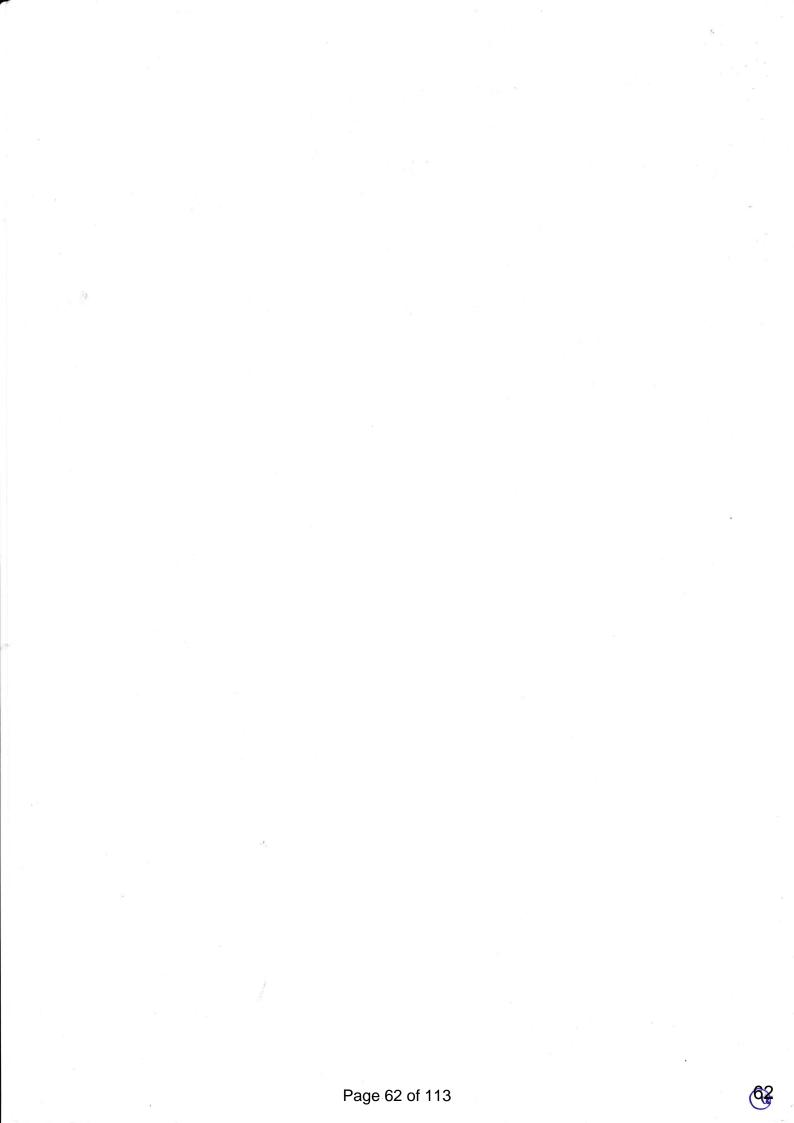

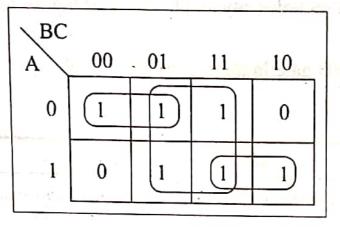

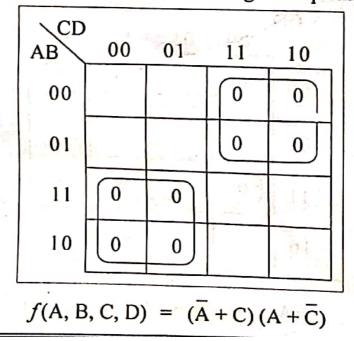

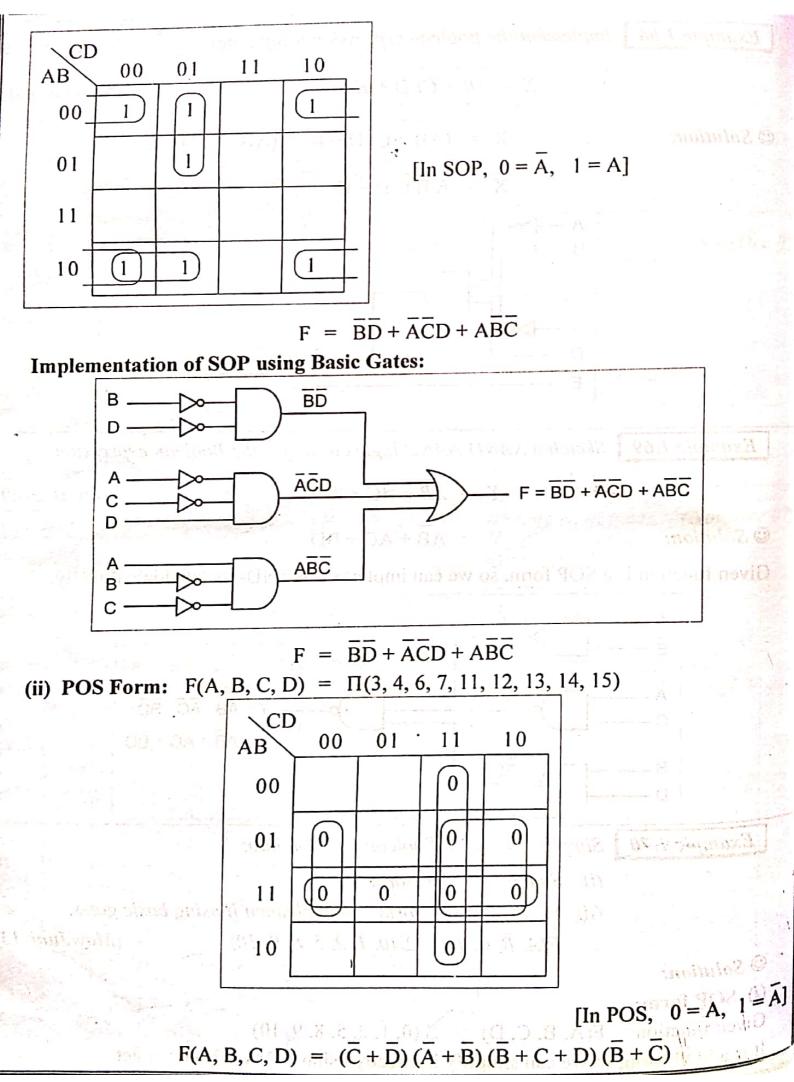

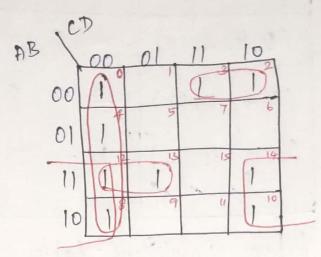

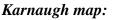

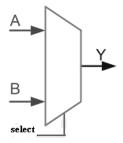

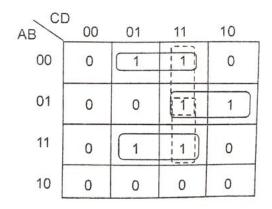

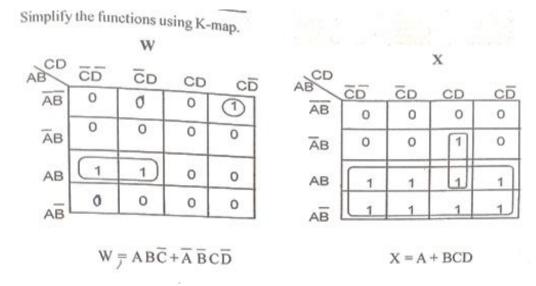

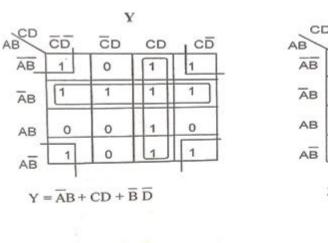

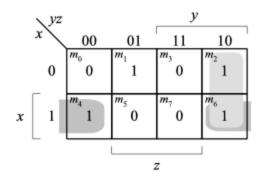

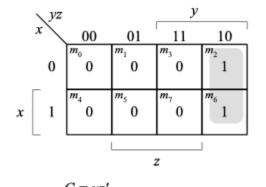

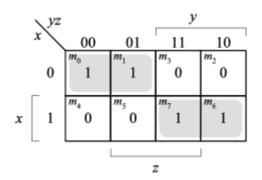

# Karnaugh Map (K-map):

- Using Boolean algebra to simplify Boolean expressions can be difficult.

- The Karnaugh map provides a simple and straight-forward method of minimizing boolean expressions which represent combinational logic circuits.

- ✤ A Karnaugh map is a pictorial method of grouping together expressions with common factors and then eliminating unwanted variables.

- ✤ A Karnaugh map is a two-dimensional truth-table. Note that the squares are numbered so that the binary representations for the numbers of two adjacent squares differ in exactly one position.

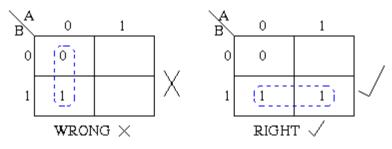

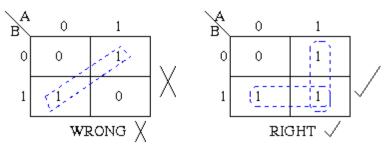

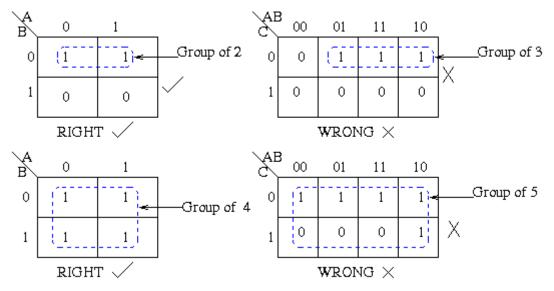

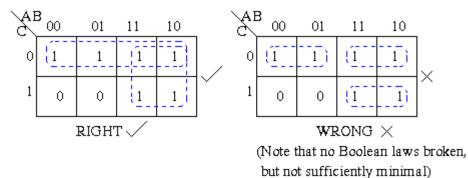

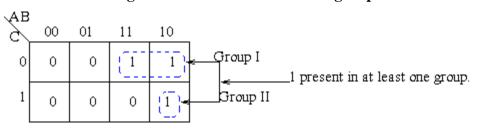

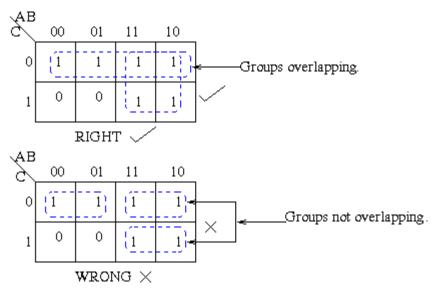

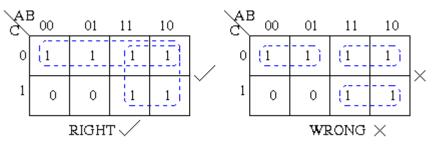

## **Rules for Grouping together adjacent cells containing 1's:**

- Groups must contain 1, 2, 4, 8, 16 (2<sup>n</sup>) cells.

- Groups must contain only 1 (and X if don't care is allowed).

- Groups may be horizontal or vertical, but not diagonal.

- Groups should be as large as possible.

- Each cell containing a 1 must be in at least one group.

- Groups may overlap.

- Groups may wrap around the table. The leftmost cell in a row may be grouped with the rightmost cell and the top cell in a column may be grouped with the bottom cell.

- There should be as few groups as possible.

## **Obtaining Product Terms**

- If A is a variable that has value 0 in all of the squares in the grouping, then the complemented form A is in the product term. "

- If A is a variable that has value 1 in all of the squares in the grouping, then the true form A is in the product term.

- If A is a variable that has value 0 for some squares in the grouping and value 1 for others, then it is not in the product term

## The Format of K-Maps:

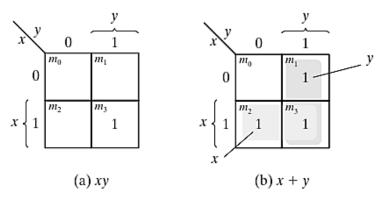

K-Maps of 2 Variables:

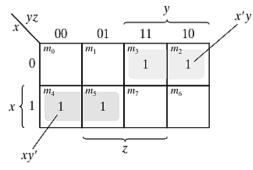

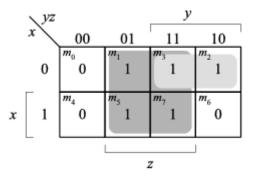

# K-Maps of 3 Variables:

Simplify the boolean function

$$F(x, y, z) = \sum (2, 3, 4, 5)$$

$$F(x, y, z) = \sum (2, 3, 4, 5) = x'y + xy'$$

unction  $F(x, y, z) = \sum 3, 4, 6, 7$

Simplify the boolean function

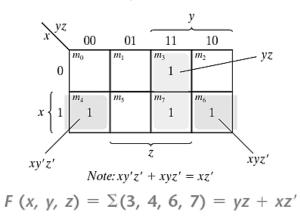

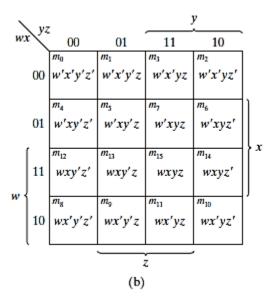

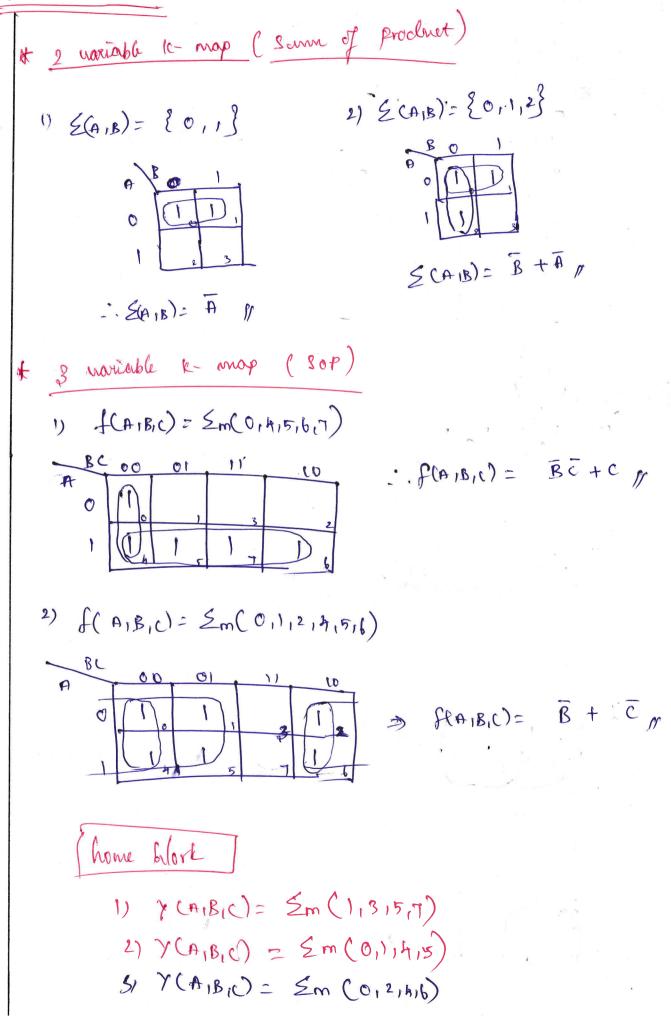

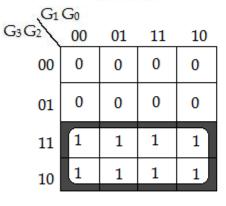

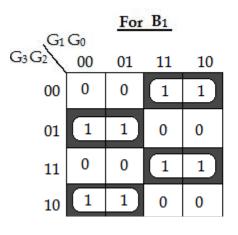

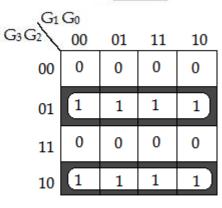

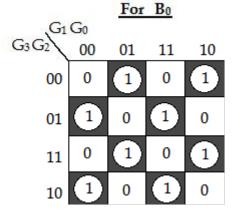

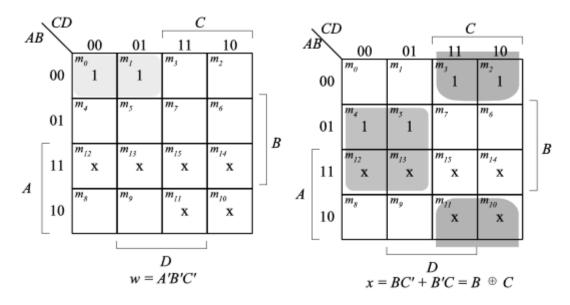

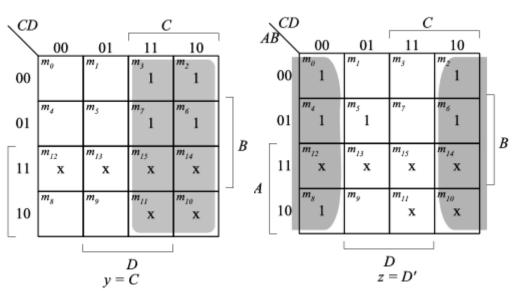

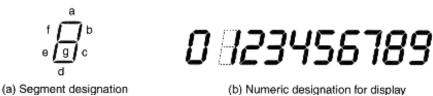

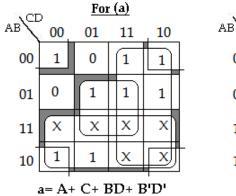

#### K-Maps of 4 Variables:

| <i>m</i> <sub>0</sub> | $m_1$                  | <i>m</i> <sub>3</sub>  | <i>m</i> <sub>2</sub>  |

|-----------------------|------------------------|------------------------|------------------------|

| <i>m</i> <sub>4</sub> | $m_5$                  | <i>m</i> <sub>7</sub>  | <i>m</i> 6             |

| m <sub>12</sub>       | <i>m</i> <sub>13</sub> | <i>m</i> <sub>15</sub> | <i>m</i> <sub>14</sub> |

| <i>m</i> <sub>8</sub> | <i>m</i> 9             | <i>m</i> <sub>11</sub> | <i>m</i> <sub>10</sub> |

(a)

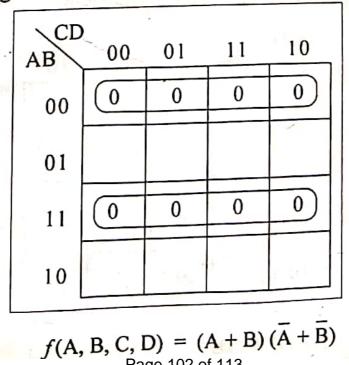

# Simplify the boolean function

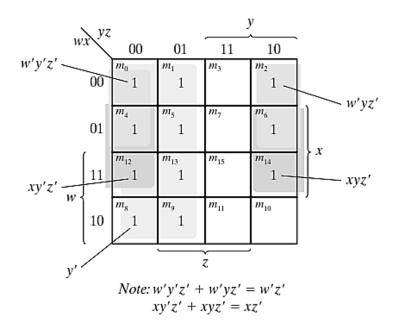

# $F(w,x, y, z) = \sum (0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14)$ (May 2011,2012, 2014,2017), (Dec 2014, Dec 2015)

$F(w, x, y, z) = \Sigma(0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14) = y' + w'z' + xz'$

Simplify the Boolean function

$$F(w, x, y, z) = \Sigma(1, 3, 7, 11, 15)$$

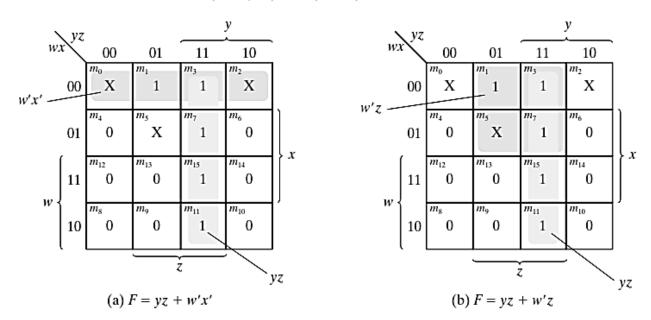

which has the don't-care conditions

$$d(w, x, y, z) = \Sigma(0, 2, 5)$$

# Note:

# Karnaugh Maps - Rules of Simplification

The Karnaugh map uses the following rules for the simplification of expressions by *grouping* together adjacent cells containing *ones*

• Groups may not include any cell containing a zero

• Groups may be horizontal or vertical, but not diagonal.

• Groups must contain 1, 2, 4, 8, or in general 2<sup>n</sup> cells. That is if n = 1, a group will contain two 1's since 2<sup>1</sup> = 2. If n = 2, a group will contain four 1's since 2<sup>2</sup> = 4.

• Each group should be as large as possible.

• Each cell containing a *one* must be in at least one group.

• Groups may overlap.

• There should be as few groups as possible, as long as this does not contradict any of the previous rules.

#### **Summary:**

- 1. No zeros allowed.

- 2. No diagonals.

- 3. Only power of 2 number of cells in each group.

- 4. Groups should be as large as possible.

- 5. Every one must be in at least one group.

- 6. Overlapping allowed.

- 7. Wrap around allowed.

- 8. Fewest number of groups possible.

# Don't care combination:

In certain digital systems, some input combinations never occur during the process of normal operation because those input conditions are guaranteed never to occur. Such input combinations are don't care conditions.

# **Completely specified functions:**

If a function is completely specified, it assumes the value 1 for some input combinations and the value 0 for others.

# Incompletely specified functions:

There are functions which assume the value 1 for some combinations and 0 for some other and either 0 or 1 for the remaining combinations. Such a functions are called incompletely specified .

# **Prime Implicants:**

A prime implicant is a product term obtained by combining the maximum possible number of adjacent squares in the map. If a minterm in a square is covered by only one prime implicant, that prime implicant is said to be essential.

## \*\*\*\*\*\*

# Quine-McCluskey (or) Tabulation Method

# Minimization of Logic functions: Steps:

- $\checkmark~$  A set of all prime implicants of the function must be obtained.

- ✓ From the set of prime implicants, a set of essential implicants must be determined by preparing a prime implicant chart.

- ✓ The minterm which are not covered by the essential implicants are taken into consideration and a minimum cover is obtained from thr remaining prime implicants.

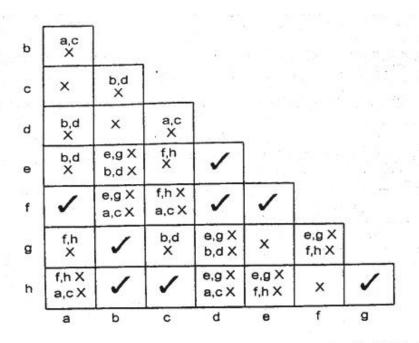

# Example:

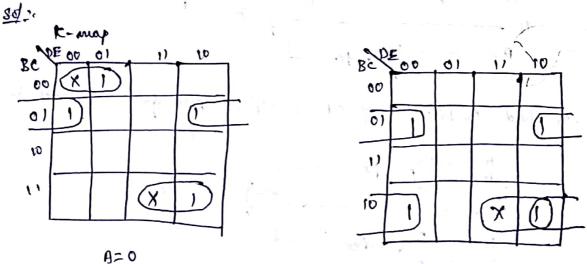

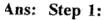

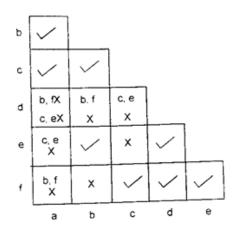

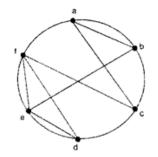

Simplify the boolean function  $F(A,B,C,D) = \sum m (1,3,6,7,8,9,10,12,14,15) + \sum m (11,13)$  using QuineMcClusky method.(May 2018, Dec 2017, Dec2016, May 2016)

| Minterms         | Binary representation | Minterms         | Binary repres | entation     |

|------------------|-----------------------|------------------|---------------|--------------|

| m <sub>1</sub>   | 0001                  | m <sub>1</sub>   | 0001          | ✓            |

| m <sub>3</sub>   | 0011                  | m <sub>8</sub>   | 1000          | ✓            |

| m <sub>6</sub>   | 0110                  | m <sub>3</sub>   | 0011          | ✓            |

| m <sub>7</sub>   | 0111                  | m <sub>6</sub>   | 0110          | ✓            |

| m <sub>8</sub>   | 1000                  | m <sub>9</sub>   | 1001          | ✓            |

| m <sub>9</sub>   | 1001                  | m <sub>10</sub>  | 1010          | ✓            |

| m <sub>10</sub>  | 1010                  | m <sub>12</sub>  | 1 1 0 0       | ✓            |

| m <sub>12</sub>  | 1100                  | m <sub>7</sub>   | 0111          | ✓            |

| m <sub>14</sub>  | 1110                  | m <sub>14</sub>  | 1110          | ✓            |

| m <sub>15</sub>  | 1111                  | dm <sub>11</sub> | 1011          | ✓            |

| dm <sub>11</sub> | 1011                  | dm <sub>13</sub> | 1101          | ✓            |

| dm <sub>13</sub> | 1101                  | m <sub>15</sub>  | 1111          | $\checkmark$ |

# Step:1

# Step:2

| Minterms | Binary representation | Minterms       | Binary representation |

|----------|-----------------------|----------------|-----------------------|

| 1, 3     | 0 0 − 1 🖌             | 1, 3, 9, 11    | -0-1                  |

| 1, 9     | -001 🗸                | 8, 9, 10, 11 🗸 | 10                    |

| 8, 9     | 100- 🗸                | 8, 10, 12, 14  | 1 — — 0               |

| 8, 10    | 10−0 ✓                |                |                       |

| 8, 12    | 1−00 ✓                | 6, 7, 14, 15 🗸 | -11-                  |

| 3, 7     | 0-11 🗸                |                |                       |

| 3, 11    | -011 🗸                | 12, 13, 14, 15 | 11                    |

| 6, 7     | 011- 🗸                |                |                       |

| 6, 14    | -110 🗸                |                |                       |

| 9, 11    | 10-1 🗸                |                |                       |

| 9, 13    | 1-01 🗸                |                |                       |

| 10, 14   | 1-10 🗸                |                |                       |

| 10, 11   | 101- 🗸                |                |                       |

| 12, 14   | 11-0 🗸                |                |                       |

| 12, 13   | 110- 🗸                |                |                       |

| 7, 15    | -111 🗸                |                |                       |

| 14, 15   | 111- 🗸                |                |                       |

# Step:3

| Prime implicants                 | Binary representation |

|----------------------------------|-----------------------|

| 1, 3, 9, 11 (B D)                | -0-1                  |

| 8, 9, 10, 11, 12, 13, 14, 15 (A) | 1                     |

| 6, 7, 14, 15 (BC)                | -11-                  |

# Step:4

| Prime<br>implicants          | m <sub>1</sub> | m <sub>3</sub> | m <sub>6</sub> | m <sub>7</sub> | m <sub>8</sub> | m <sub>9</sub> | m <sub>10</sub> | m <sub>12</sub> | m <sub>14</sub> | m <sub>15</sub> | dm <sub>11</sub> | dm <sub>13</sub> |

|------------------------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|-----------------|-----------------|------------------|------------------|

| 1, 3, 9, 11 (BD)             | $\odot$        | $\odot$        |                |                |                | $\odot$        |                 |                 |                 |                 | $\odot$          |                  |

| 8, 9, 10, 11, 12, 13, 14, 15 |                |                |                |                | $\odot$        | $\odot$        | $\odot$         | $\odot$         | $\odot$         | $\odot$         | $\odot$          | $\odot$          |

| 6, 7, 14, 15 (BC)            |                |                | $\odot$        | $\odot$        |                |                |                 |                 | $\odot$         | $\odot$         |                  |                  |

$: F(A, B, C, D) = \overline{B}D + A + BC$

#### \*\*\*\*\*

[NOV/DEC 2021]

\* Simplify the Boolean expression, 2y +2(WZ+WZ') to minimum number of literals. [Nov/DEC-2021] xy + x(wz + wz') $= xy + x \omega (z + z') \int z + z' = 1$ = xy+xw = x(y+w)

# 1. Define Digital Systems. Give an example.

A system which is processing discrete or digital signal is called as Digital System. Digital computer is the best example of a digital system.

# 2. What is meant by (i) bit, (ii) byte, (iii) Nibble?

- (i) A binary digit is called bit.

- (ii) A group of 8 bits are called Byte

- (iii) In binary number a group of four bits called Nibble.

# 3. Define Radix.

Radix specifies the number of symbols used for the corresponding number system. .

## 4. List the number systems used in digital systems.

- i) Decimal Number system i

- ii) Binary Number system

- iii) Octal Number system

- iv) Hexadecimal Number system

# 5. Why is a hexadecimal number system called as an alpha numeric number system?

Hexadecimal number system has the base as 16 and therefore it requires 16 distinct symbols to represent the numbers. These are numerals 0 to 9 and alphabets A to F. Since both numeric digitals and alphabets are used to represent the digits in hexadecimal number system, it is called as an alphanumeric number system.

## 6. What is 1's and 2's complement?

- ✓ The 1's complement of a binary number is the number that results when we change all 1's to zeros and the zeros to ones.

- ✓ The 2's complement is the binary number that results when we add 1 to the 1's complement. It is used to represent negative numbers.

# 7. Convert Binary to hex decimal.

1011 0010 1111<sub>2</sub> = (1011) (0010) (1111)<sub>2</sub> = B 2  $F_{16}$

## 8. Convert hex decimal to octal.

| Hexadecimal         | Octal                      |

|---------------------|----------------------------|

| (5A8) <sub>16</sub> | = 0101 1010 1000 (Binary)  |

|                     | = 010 110 101 000 (Binary) |

| Result              | = 2650 (Octal)             |

#### 9. Convert binary to octal and vice versa with an example.

Binary to octal:

Example:

$$100\,111\,0102 = (100)\,(111)\,(010)2 = 4\,7\,28$$

Octal to Binary:

Sol:

## **10.** Find **2**'s complement of (1001)<sub>2</sub>.

| 1001<br>0110← | number<br>1's complement |

|---------------|--------------------------|

| + 1           | add 1                    |

| 0111          |                          |

#### 11. Illustrate Diminished Radix Complement with an example?

(Dec-2009)

Given a number N in base r having n digits, the (r-1)'s complement of N, i.e., its diminished radix complement,

is defined as (m-1) - N.

The 9's complement of 546700 is 999999 - 546700 = 453299. The 9's complement of 012398 is 999999 - 012398 = 987601.

## **12. What is BCD code (8421)?**

A decimal number in BCD(8421) is the same as its equivalent binary number only when the number is between 0 and 9. A BCD number greater than 10 looks different from its equivalent binary number, even though both contain 1's and 0's. Moreover, the binary combinations 1010 through 1111 are not used and have no meaning in BCD.

# **13. BCD addition:** 184 + 576 = ?

| BCD        | 1     | 1     |      |      |

|------------|-------|-------|------|------|

|            | 0001  | 1000  | 0100 | 184  |

|            | +0101 | 0111  | 0110 | +576 |

| Binary sum | 0111  | 10000 | 1010 |      |

| Add 6      |       | 0110  | 0110 |      |

| BCD sum    | 0111  | 0110  | 0000 | 760  |

## 14. What is excess-3 code?

This code assignment is obtained from the corresponding value of 4-bit binary code after adding 3 to the given decimal digit.

**Example:** 1000 of 8421 (BCD) = 1011 in Excess-3.

# 15. What is gray code?

The gray code belongs to a class of codes called minimum change codes, in which only one bit in the code changes when moving from one code to the next.

b(1) b(2) b(3) b(4) b(5) g(1) b(1) xor g(2) b(2) xor g(3) b(3) xor g(4) b(4) xor g(5)

#### 19. What is Error detecting codes?

When data is transmitted from one point to another, like in wireless transmission, or it is just stored, like in hard disks and memories, there are chances that data may get corrupted. To detect these data errors, we use special codes, which are error detection codes.

#### 20. What is Error correcting code

Error-correcting codes not only detect errors, but also correct them. This is used normally in Satellite communication, where turn-around delay is very high as is the probability of data getting corrupt.

#### 21. What is Hamming codes?

Hamming code adds a minimum number of bits to the data transmitted in a noisy channel, to be able to correct every possible one-bit error.

It can detect (not correct) two-bit errors and cannot distinguish between 1-bit and 2bits inconsistencies. It can't - in general - detect 3(or more)-bits errors.

#### 22. What are the Two types of parity?

**-Even parity:** Checks if there is an even number of ones; if so, parity bit is zero. When the number of one's is odd then parity bit is set to 1.

**-Odd Parity:** Checks if there is an odd number of ones; if so, parity bit is zero. When the number of one's is even then parity bit is set to 1.

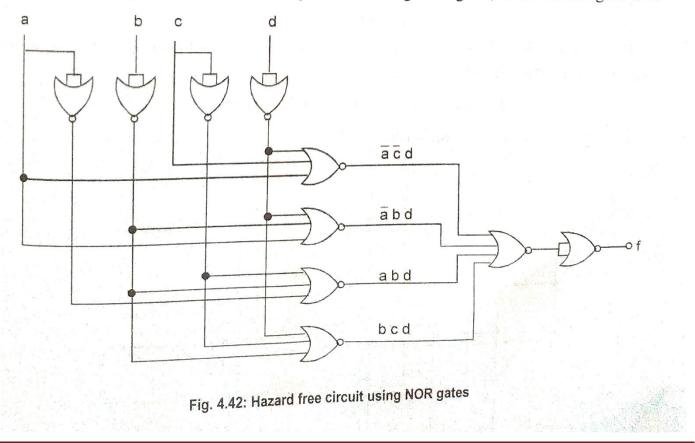

23. What is Parity Checker / Generator?

## (Dec 2018)

The circuit that generates the parity bit in the transmitter is called a parity generator. The circuit that checks the parity in the receiver is called a parity checker.

# 24. What is EBCDIC codes?

- > EBCDIC stands for *Extended Binary Coded Decimal Interchange*.

- For the different alphanumeric characters the code grouping in this code is different from the ASCII code. It is actually an 8-bit code and a ninth bit is added as the parity bit.

## 25. What is meant by Boolean algebra & Boolean Expression?

A system of algebra that operates on Boolean variables are called Boolean algebra.

The binary nature of Boolean algebra makes it useful for analysis, simplification and design of logic circuits are called Boolean Expression.

## 26. What are basic properties of Boolean algebra? (Dec 2016)

The basic properties of Boolean algebra are commutative property, associative property and distributive Property

#### 27. State the associative property of Boolean algebra.

The associative property of Boolean algebra states that the OR ing of several variables results in the same

regardless of the grouping of the variables. The associative property is stated as follows:

$$A+(B+C)=(A+B)+C$$

, ii).  $A(BC)=(AB)C$

#### 28. State the commutative property of Boolean algebra.

The commutative property states that the order in which the variables are OR ed makes no difference. The

commutative property is i). A+B=B+A ii). AB=BA

#### 29. State the distributive property of Boolean algebra.

The distributive property states that AND ing several variables and OR ing the result with a single variable

is equivalent to OR ing the single variable with each of the several variables and then AND ing the sums.

The distributive property is

i). A+BC = (A+B)(A+C) ii). A(B+C) = AB + AC

#### **30. State De Morgan's theorem. (Dec 2019)** (April/May 2011,2010,2013) Dec- 2017 ,(May 2018)

De Morgan suggested two theorems that form important part of Boolean algebra. They are

1) The complement of a product is equal to the sum of the complements.(A . B)' = A' + B'

2) The complement of a sum term is equal to the product of the complements.(A + B)' = A'B'

## **31. Define Duality Theorem.**

Duality property states that every algebraic expression deducible from the postulates of Boolean algebra remains valid if the operators and identity elements are interchanged. If the dual of an algebraic expression is desired, we simply interchange OR and AND operators and replace 1's by 0's and 0's by 1's.

## 32. List the important postulates of Boolean theorems.

The following are the important postulates of Boolean algebra:

1.1.1 = 1,0+0 = 0.2.1.0 = 0.1 = 0,0+1 = 1+0 = 1.3.0.0 = 0,1+1 = 1.

4. 1' = 0 and 0' = 1.

# 33. What is Boolean algebra?

Boolean algebra is an algebra that deals with binary variables and logic operations. A Boolean function described by an algebraic expression consists of binary variables, the constants 0 and 1, and the logic operation symbols.

#### 34. What are the two forms of Boolean expression?

The two forms of Boolean expressions are:

i). Sum of Products Form

ii).Product of Sum Form

# 35. Define Minterm & Maxterm.

#### (May 2018)

The products of Boolean expression where all possible variables appear once in complement or un complement variables are called Minterm.

A sum terms in a Boolean expression where all possible variables appear once, in complement or un omplement form are called Maxterm.

# **36. Define Product term.**

The AND function is referred to as a product. The variable in a product term can appear either in complementary or uncomplimentary form. **Example: ABC'**

# 37. Define Sum term.

The OR function is referred to as a Sum. The variable in a sum term can appear either in complementary or uncomplimentary form. **Example:** A+B+C'

# 38. Define Sum of Product (SOP).

The logical sum of two or more logical product terms is called sum of product expression. It is basically an OR operation of AND operated variables. **Example: Y=AB+BC+CA**

#### **39. Define Product of Sum (POS).**

The logical product of two or more logical sum terms is called product of sum expression. It is basically an AND operation of OR operated variables. **Example:** Y=(A+B).(B+C).(C+A)

# 40. What is Canonical form?

Boolean functions expressed as a sum of minterms or product of maxterms are said to be in *canonical form*.

# 41. What is Canonical SOP Expression?

The minterms whose sum defines the Boolean function are those which give the 1's of the function in a truth table.

# 42. What is Canonical POS Expression?

The Maxterms whose product defines the Boolean function are those which give the 1's of the function in a truth table.

#### 43. What is meant by karnaugh map or K-Map method?

A kamaugh map or k map is a pictorial form of truth table, in which the map diagram is made up of cells, with each cell representing one minterm or maxterm of the function. This method provides a simple straight forward procedure for minimizing Boolean function.

#### 44. Define Cell.

The smallest unit of a karnaugh map, corresponding to one rows of a truth table. The input variables are the cells coordinates and the output variable is the cells contents.

## 45. Define Pair, Quad, and Octet.

- i). Pair: A group of two adjacent cells in a karnaugh map. A pair cancels one variable in a K-Map simplification.

- ii). Quad: A group of four adjacent cells in a karnaugh map. A quad cancels two variables in a K-Map simplification.

- iii).Octet: A group of eight adjacent cells in a karnaugh map. A pair cancels three variable in a K-Map simplification.

#### 46. What are called don't care conditions?

In some logic circuits certain input conditions never occur, therefore the corresponding output never appears. In such cases the output level is not defined, it can be either high or low.

These output levels are indicated by 'X' or 'd' in the truth tables and are called don't care conditions or incompletely specified functions.

#### 47. State the limitations of karnaugh map.

- i. It is limited to six variable maps (i.e.) more than six variable involving expressions are not reduced.

- ii. The map method is restricted in its capability since they are useful for simplifying only Boolean expression represented in standard form.

## (April/May 2013)

(Dec 2017

## (May 2014)

(May 2016)

# 48. list out the advantages and disadvantages of K-map method.

# The advantages of the K-map method are:

- i). It is a fast method for simplifying expression up to four variables

- ii). It gives a visual method of logic simplification.

- iii). Prime implicants and essential prime implicants are identified fast.

- iv). Suitable for both SOP and POS forms of reduction

- v). It is more suitable for class room teachings on logic simplification.

# The disadvantages of the K-map method are:

- i). It is not suitable for computer reduction .

- ii). K-maps are not suitable when the number of variables involved exceed four

- iii). Care must be taken to fill in every cell with the relevant entry, such as a 0, 1 (or) don't care terms.

# 49. What is tabulation method?

A method involving an exhaustive tabular search method for the minimum expression to solve a Boolean equation for more variables is called as a tabulation method.

# 50. What is a prime implicant?

A prime implicant is a product term obtained by combining the maximum possible number of adjacent squares in the map. They cannot be reduced further. (Or) A prime implicant is a group of minterms which cannot be combined with any other minterm or groups.

# 51. What is an essential prime implicant?

The Essential Prime Implicant is a prime implicant in which one or more minterms are unique, it contains at least one minterm which is not contained in any other prime implicant.

# 52. List out the advantages and disadvantages of Quine-Mc Cluskeymethod? (May 2015) The advantages of Quine-Mc Cluskey method are:

i). This is suitable when the number of variables exceed four.

ii). Digital computers can be used to obtain the solution fast.

iii). Essential prime implicants, which are not evident in K-map, can be clearly seen in the final results.

# The disadvantages are:

- i). Lengthy procedure than K-map.

- ii). Requires several grouping and steps as compared to K-map.

- iii). It is much slower.

- iv). No visual identification of reduction process.

- v). The Quine Mc Cluskey method is essentially a computer reduction method.

# 53. What is a Logic gate?

Logic gates are the basic elements that make up a digital system. The electronic gate is a circuit that is able to operate on a number of binary inputs in order to perform a particular logical function.

# 54. Which gates are called as the universal gates? What are its advantages?

The NAND and NOR gates are called as the universal gates. These gates are used to perform any type of logic application.

## 55. Write the applications of gray code.

Used in telegraphy, robust communication and error detection & correction.

**56.** Show that the logical sum of all minterms of a Boolean function of 2 variables is 1 The combinations of minterms are A'B'+A'B+AB'+AB (Nov/Dec 2009)

$$=A'(B+B')+A(B+B')$$

$$=A+A'$$

57. Find the complement of the functions F1 = x'yz' + x'y'z and F2 = x(y'z' + yz). (Dec 2015) By applying De-Morgan's theorem.

$$F1' = (x'yz' + x'y'z)' = (x'yz')'(x'y'z)' = (x + y' + z)(x + y + z')$$

$$F2' = [x(y'z' + yz)]' = x' + (y'z' + yz)'$$

$$= x' + (y'z')'(yz)'$$

$$= x' + (y + z)(y' + z')$$

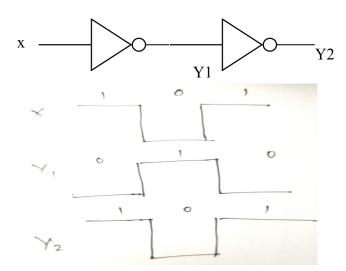

58. Sketch the the waveform of each inverter output in the given diagram. (Dec 2017)

59. Convert decimal 8723 to both BCD and ASCII code for ASCII an even parity bit is to be appended at left. (Dec 2019)

Decimal - 8723 BCD - 1000011100100011 ASCII- 11000011100100011

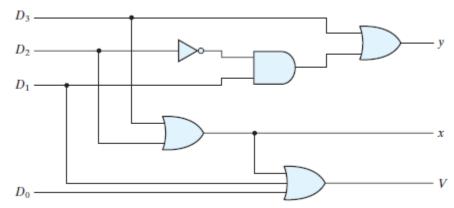

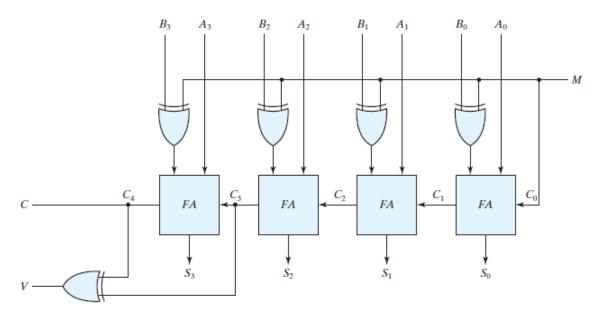

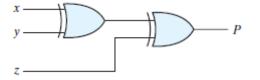

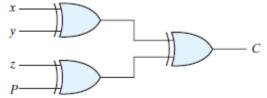

# UNIT-P

[ MAY 2019] 59. What is the largest bimovy number that can be Expressed with 14 bits? Determine the equinalent decimal and here decimal mumbers. [NOV/DEC 2021] sol: . largest Binary unber in 14 bits 14111111111111111 Dectinal :. -> 0× 2° = 4 3 Z 8  $x_{2}^{4} = 16$  $1 \times 2^{5} = 32$ 1×26 = 64 1×27 = 128 + 1×28 = 256 1×27 = 512 + 1×210 = 1024 > 1×2" = 20 18 - 1x 212 = 4096 -1 1× 213 = 8192 16,363 Hera Decimal: 00 11/11 11/11 11/11 11 FFF 3 The answer is : SFFF

[HIAY-2019]

2. Find the complement of F= Wx + yz and then show that FF=0 501: F= WX+YZ 2. complement. F'= WX+YZ = wx + yz  $F = (\overline{w} + \overline{x}) \cdot (\overline{y} + \overline{z}) ,$ show that FF=0  $= (w_{x+y_z})(\overline{w}+\overline{x}) \cdot (\overline{y}+\overline{z})$  $= (w \overline{w} x + w x \overline{x} + \overline{w} y z + \overline{x} y z) \cdot (\overline{y} + \overline{z})$ A-A=0 =  $(\overline{\omega}yz + \overline{x}yz) \cdot (\overline{y} + \overline{z})$  $= \overline{w} y \overline{y} \overline{z} + \overline{x} \overline{y} \overline{y} \overline{z} + \overline{w} \overline{y} \overline{z} \overline{z} + \overline{x} \overline{y} \overline{z} \overline{z}$ FF = '0' cunce provid · · · · • 1 - 1 - 1 - 1 A 14 C 16 1 - C., in it with a ÷ . - 1 - C - 🔅

UNIT-I NUMBER CONVERSION Problems to be discussed. Decimal to Binary \* (48,16) = ( )2 \* (48) 10 = ()2  $2 | \frac{18}{23 - 0} = 0.16 \times 2 = 0.32 \Rightarrow 0$  $2 | \frac{48}{2} | \frac{24}{-0} - 0 \\ 2 | \frac{12}{-0} - 0 \\ 2 | \frac{6}{-0} - 0 \\ 2 | \frac{3-0}{-0}$  $2 | \frac{12 - 0}{2 | 12 - 0} = 0.32 \times 2 = 0.64 \Rightarrow 0$   $2 | \frac{12 - 0}{2 | 6 - 0} = 0.64 \times 2 = 1.28 \Rightarrow 1.50$   $2 | \frac{3 - 0}{2 | - 1} = 0.28 \times 2 = 0.56 \Rightarrow 0$ ~ (48)10 = ( 110000)2 // - (48.16)10 = (110000.0010)2 / (2) Decimal to octal \* (A 0.72) = () 0.72 18 = 5.76 = 5 8 40 0.76×8 = 6.08 => 6 0.08 ×8= 0.64 > 0 0.64×8 = 5.12 = 5 -· ( 40.72) = ( 50.5605) 8 11 10 3 3) Decimal to hera decimal \* (82.15)10 = ()16 0.15×16 = 2.40 => 2 16 32  $0.40 \times 16 = 6.40 \Rightarrow 6$ 0.40 x16 = 6.40 => 6 0.40 × 16 = 6.40 = 6  $-(32.15)_{10} = (20.266)_{16}$

I·

(\*) Bimary to Decimal

\*

$$(100110 \cdot 10)_{2} = (-)_{10}$$

$10 \quad 0 \quad 11 \quad 0 \quad 1x_{2} = (-)_{10}$

$10 \quad 0 \quad 11 \quad 0 \quad 1x_{2} = (-)_{10}$

$1x_{2} = (-)_{10} \quad 1x_{2} = 2$

$1x_{2} = (-)_{10} \quad 1x_{2} = (-)_{1$

(1) here defined to Binary

\* (17B. C2)<sub>11</sub> = C2

$$\frac{1}{2}$$

$\frac{7}{4}$   $\frac{1}{4}$   $\frac{1}{4}$   $\frac{1}{4}$   $\frac{1}{4}$